CS5490-ISZR View Datasheet(PDF) - Cirrus Logic

Part Name

Description

MFG CO.

CS5490-ISZR Datasheet PDF : 56 Pages

| |||

CS5490

6) If the phase offset is negative, then the delay should

be added only to the current channel. Otherwise, add

more delay to the voltage channel than to the current

channel to compensate for a positive phase offset.

Once the phase offset is known, the CPCC and FPCC

bits for that channel are calculated and programmed in

the PC register.

CPCC bits are used if either

• The phase offset is more than 1 output word rate

(OWR) sample.

• More delay is needed on the voltage channel.

The compensation resolution is 0.008789° at 50Hz and

0.010547° at 60Hz at an OWR of 4000Hz.

7.3 Temperature Sensor Calibration

Temperature sensor calibration involves the adjustment

of two parameters: temperature gain (TGAIN) and

temperature offset (TOFF). Before calibration, TGAIN

must be set to 1.0 (0x 01 0000), and TOFF must be set

to 0.0 (0x 00 0000).

7.3.1 Temperature Offset and Gain Calibration

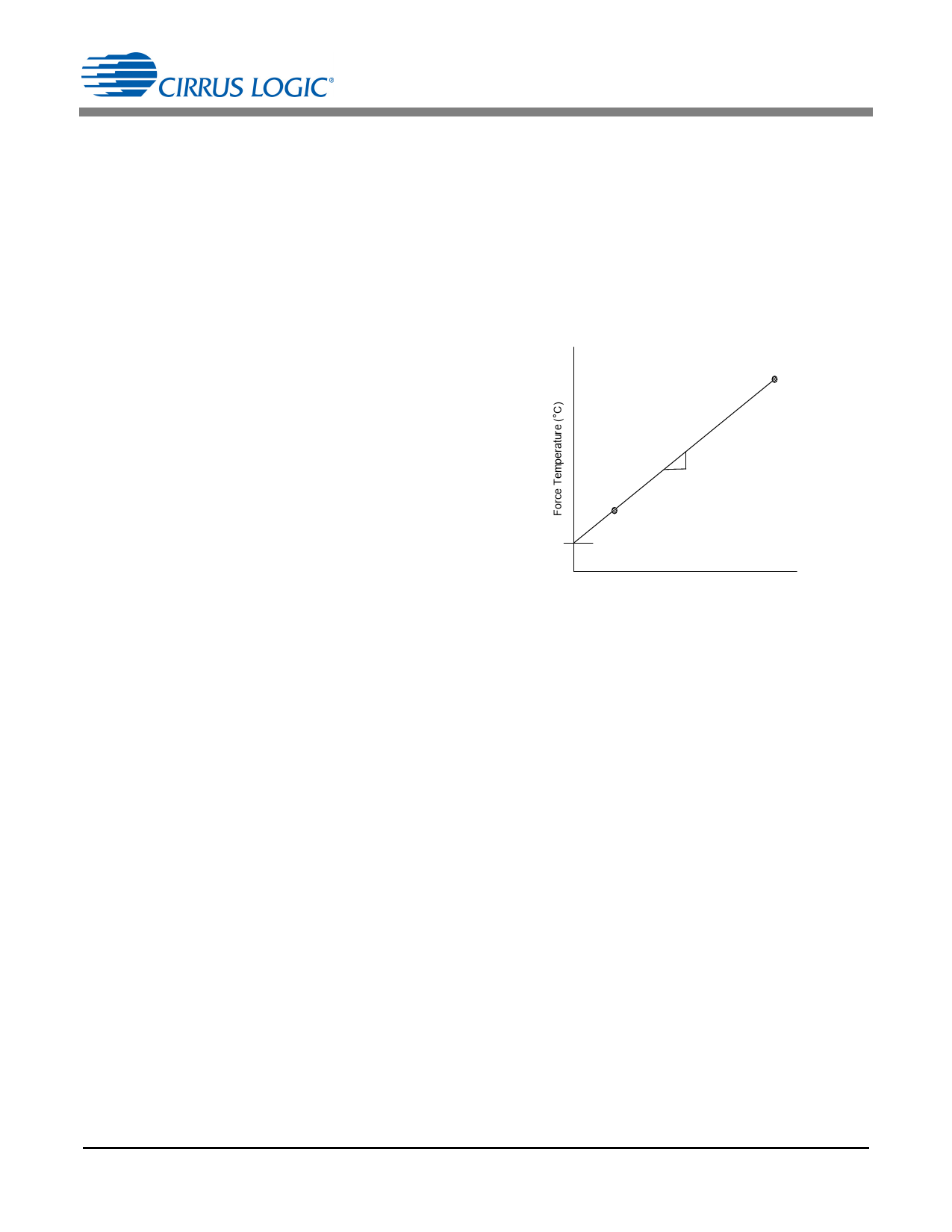

To obtain the optimal temperature offset (TOFF) register

value and temperature (TGAIN) register value, it is

necessary to measure the temperature (T) register at a

minimum of two points (T1 and T2) across the meter

operating temperature range. The two temperature

points must be far enough apart to yield reasonable

accuracy, for example 25°C and 85°C. Obtain a linear

fit of these points (y = m x + b ), where the slope (m)

and intercept (b) can be obtained.

T2

Y = m • x +b

m

T1

b

T Register Value

Figure 20. T Register vs. Force Temp

TOFF and TGAIN are calculated using the equations

below:

TOFF = m-b---

TGAIN = m

DS982F2

53