CS8422-DNZR View Datasheet(PDF) - Cirrus Logic

Part Name

Description

MFG CO.

CS8422-DNZR Datasheet PDF : 82 Pages

| |||

CS8422

0101

0110

0111

1000

384

512

768

1024

48

96

64

128

48

96

64

128

Table 8. ISCLK/ILRCK Ratios and SISF Settings

SIFSEL[2:0] - Serial audio input data format

000 - Left-Justified, up to 24-bit data

001 - I²S, up to 24-bit data

010 - Right-Justified, 24-bit data

011 - Right-Justified, 20-bit data

100 - Right-Justified, 18-bit data

101 - Right-Justified, 16-bit data

110, 111 - Reserved

11.12 Serial Audio Output Data Format - SDOUT1 (0Ch)

7

6

5

4

3

2

SOMS1

SOSF1

SORES1_1 SORES1_0 SOFSEL1_1 SOFSEL1_0

0

0

0

0

0

0

1

TDM1

0

0

TDM0

0

SOMS1 - Master/Slave Mode Selector

0 - Serial audio output port is in slave mode. OSCLK and OLRCK are inputs.

1 - Serial audio output port is in master mode. OSCLK and OLRCK are outputs.

SOSF1 - OSCLK1 Frequency. Valid only in master mode (SOMS1 = 1). If the SRC is selected as the source

for SDOUT1 (SDOUT1[1:0] = 00 in register 0Ah), then the master clock (MCLK) is the SAO MCLK (as se-

lected by the SAO_MCLK bit in register 08h). If the AES3 receiver is selected as the source for SDOUT1

(SDOUT1[1:0] = 01 in register 0Ah), then the MCLK is RMCK. Should be changed when PDN = 1. See

Table 9 for details. Note: If serial output 1 is in master mode and sourced directly by the serial input port,

SAI_CLK[3:0] determines the MCLK/OLRCK1 ratio.

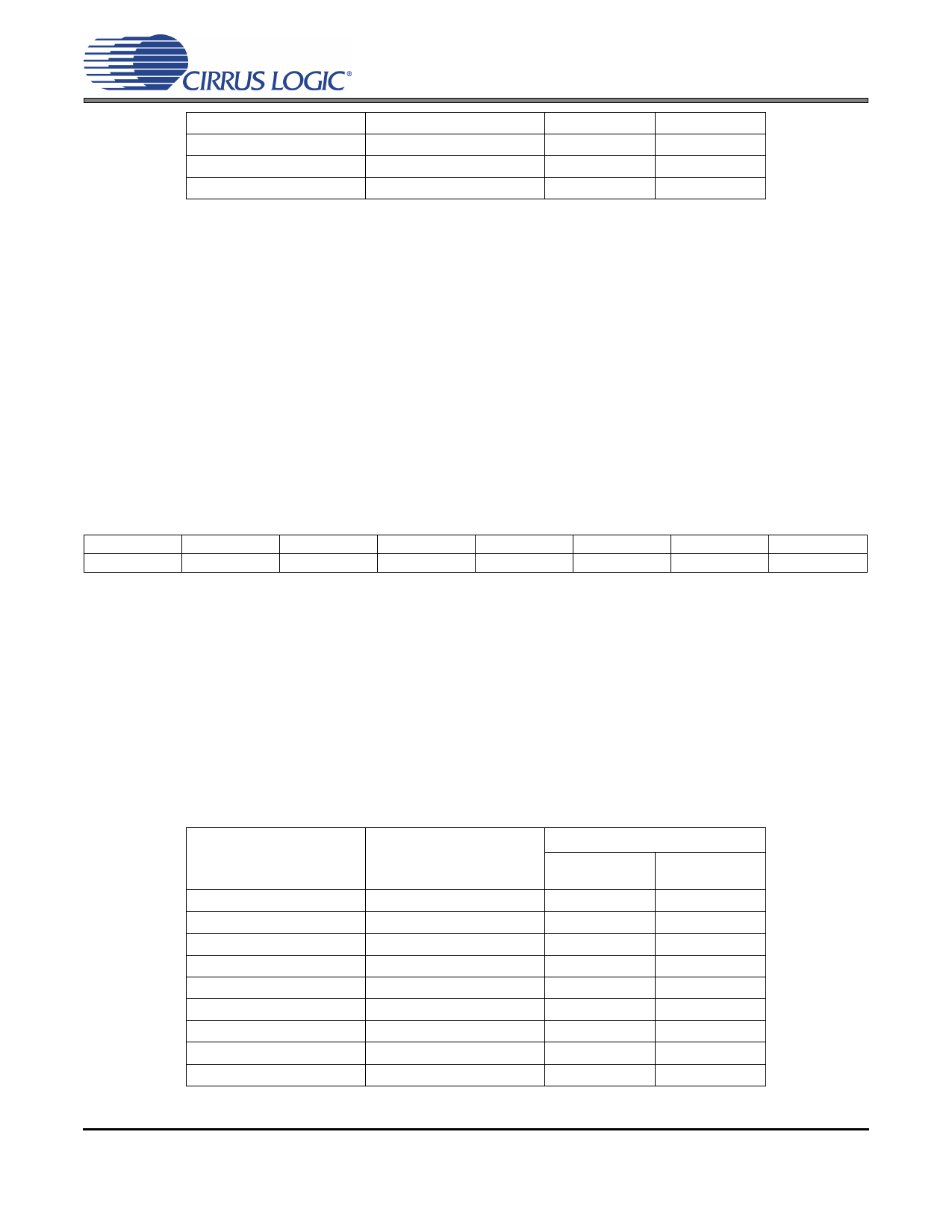

SAO_CLK[3:0],

SAI_CLK[3:0], or

RMCK[3:0]

0000

0001

0010

0011

0100

0101

0110

0111

1000

MCLK/OLRCK1 Ratio

64

96

128

192

256

384

512

768

1024

OSCLK1/OLRCK1 Ratio

SOSF1 = 0 SOSF1 = 1

64

INVALID

48

96

64

128

48

96

64

128

48

96

64

128

48

96

64

128

Table 9. OSCLK1/OLRCK1 Ratios and SOSF1 Settings

54

DS692F1