# **YDA143**

# **D-3M**

#### STEREO 15W DIGITAL AUDIO POWER AMPLIFIER

#### ■ Overview

YDA143 (D-3M) is a high efficient digital audio power amplifier IC that operates with a single 12V power supply.

An audio power amplifier with a maximum output of 15W ( $R_L$ =4 $\Omega$ ) × 2ch can be configured with one chip.

YDA143 has a "Pure Pulse Direct Speaker Drive Circuit" which directly drives speakers while reducing distortion of pulse output signal and reducing noise on the signal, and realizes the highest standard low distortion rate characteristics and low noise characteristics as 15W-class of output digital amplifier IC.

In addition, circuit design with fewer external parts can be made depend on the condition of use because corresponds to filter less.

YDA143 has 50mW ( $R_1$ =32 $\Omega$ ) × 2ch Class AB headphone amplifiers.

YDA143 provides Over-current protection function for speaker output terminals, IC thermal protection function, and POP noise reduction function as well as power-down function and output mute function.

#### ■ Features

#### **Digital Amplifier**

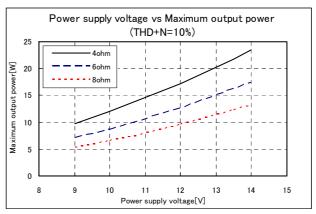

- •Continuous maximum output 15 W×2ch (V<sub>DDP</sub>=12.0V, R<sub>L</sub>=4Ω, THD+N=10%)

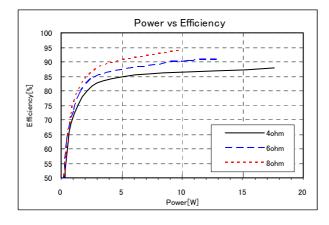

- Efficiency

87 %  $(V_{DDP}=12.0V, R_L=4\Omega, Po=15W)$

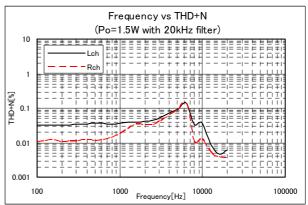

• Distortion Rate (THD+N)

0.04 % (V<sub>DDP</sub>=12.0V, R<sub>L</sub>=4 $\Omega$ , Po=1.5W)

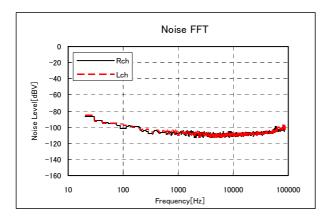

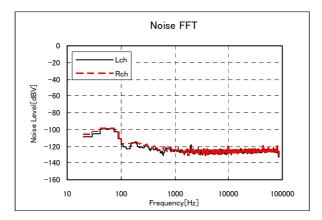

·S/N Ratio

103dB  $(V_{DDP}=12.0V, R_L=4\Omega, Po=15W, GAIN[1:0]=H,H)$

Channel Separation

-65dB  $(V_{DDP}=12.0V, R_L=4\Omega, GAIN[1:0]=H,H)$

#### Class AB Headphone Amplifier

· Maximum output

50mW×2ch (V<sub>DDP</sub>=12.0V, R<sub>L</sub>=32Ω, THD+N=10 %)

•Distortion Rate(THD+N)

0.01% (V<sub>DDP</sub>=12.0V, R<sub>L</sub>=32 $\Omega$ , P<sub>ho</sub>=25mW)

·S/N Ratio

95dB  $(V_{DDP}=12.0V, R_L=32\Omega, P_{ho}=50mW, GAIN[1:0]=H,H)$

#### Others

- Operating power supply range 9.0V to 13.5V

- Multi-channel synchronizing operation by Master/Slave switching function

- Carrier frequency switching function 524kHz/466kHz

- ·Sleep function with SLEEPN terminal

- ·Output muting function with MUTEN terminal

- ·Over-current protection function

- Thermal protection function

- •Clock stop protection function

- Pop noise reduction function

- ·Analog input/BTL (Bridge-Tied Load) output

- ·Lead-free 52-pin SSOP (YDA143-EZ)

YAMAHA CORPORATION

YDA143 CATALOG CATALOG No.:LSI-4DA143A20

2006.6

# ■Terminal configuration

|              |            |  |    | ` |                |

|--------------|------------|--|----|---|----------------|

|              |            |  |    |   |                |

| HPOR         | <b>ቯ</b> 1 |  | 52 |   | HPOL           |

| AVSS         | 2          |  | 51 |   | REFA           |

| VSSBGR       | 3          |  | 50 |   | <b>PVDDREG</b> |

| VREFR        | 4          |  | 49 |   | VREFL          |

| INR _        | 5          |  | 48 |   | INL            |

| MUTEN        | 6          |  | 47 |   | HP             |

| NC _         | 7          |  | 46 |   | NC             |

| VSS _        | 8          |  | 45 |   | VSS            |

| VSS _        | 9          |  | 44 |   | VSS            |

| PVDDPR       | 10         |  | 43 |   | PVDDPL         |

| PVDDPR       | 11         |  | 42 |   | PVDDPL         |

| OUTPR _      | 12         |  | 41 |   | OUTPL          |

| VSS _        | 13         |  | 40 |   | VSS            |

| PVSSR        | 14         |  | 39 |   | PVSSL          |

| OUTMR _      | 15         |  | 38 |   | OUTML          |

| PVDDMR       | 16         |  | 37 |   | PVDDML         |

| PVDDMR       | 17         |  | 36 |   | PVDDML         |

| VSS _        | 18         |  | 35 |   | VSS            |

| VSS _        | 19         |  | 34 |   | VSS            |

| NC _         | 20         |  | 33 |   | NC             |

| PROTN        | 21         |  | 32 |   | GAIN1          |

| SLEEPN       | 22         |  | 31 |   | GAIN0          |

| DVSS         | 23         |  | 30 |   | MODE2          |

| CKIO _       | 24         |  | 29 |   | MODE1          |

| XO $\square$ | 25         |  | 28 |   | MODE0          |

| XI 🗀         | 26         |  | 27 |   | DVDD           |

|              |            |  |    |   |                |

|              |            |  |    | • |                |

<52-pin SSOP Top View>

# ■Terminal function

| No. | Name    | I/O      | Function                                                      | Voltage tolerance |

|-----|---------|----------|---------------------------------------------------------------|-------------------|

| 1   | HPOR    | 0        | R-ch Headphone Output terminal                                | LV                |

| 2   | AVSS    | GND      | 5V Analog Ground terminal                                     | -                 |

| 3   | VSSBGR  | GND      | Ground terminal for Reference Voltage Supply                  | -                 |

| 4   | VREFR   | 0        | R-ch Reference Voltage terminal (with external capacitor)     | LV                |

| 5   | INR     |          | R-ch Analog Signal Input terminal                             | LV                |

| 6   | MUTEN   |          | Mute Control terminal                                         | LV                |

| 7   | NC      | -        | No Connection                                                 | -                 |

| 8   | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 9   | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 10  | PVDDPR  | Power    | R-ch 12V-line VDD terminal                                    | HV                |

| 11  | PVDDPR  | Power    | R-ch 12V-line VDD terminal                                    | HV                |

| 12  | OUTPR   | 0        | R-ch Positive Side Output terminal                            | HV                |

| 13  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 14  | PVSSR   | GND      | R-ch 12V-line VSS terminal                                    | -                 |

| 15  | OUTMR   | 0        | R-ch Negative Side Output terminal                            | HV                |

| 16  | PVDDMR  | Power    | R-ch 12V-line VDD terminal                                    | HV                |

| 17  | PVDDMR  | Power    | R-ch 12V-line VDD terminal                                    | HV                |

| 18  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 19  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | _                 |

| 20  | NC      | -        | No Connection                                                 | _                 |

| 21  | PROTN   | O/D      | Warning Signal Output terminal (O/D)                          | HV                |

| 22  | SLEEPN  | I        | Sleep Control terminal                                        | HV                |

| 23  | DVSS    | GND      | Digital Ground terminal                                       | -                 |

| 24  | CKIO    | 1/0      | Clock Input/Output terminal                                   | LV                |

| 25  | XO      | 0        | CERALOCK connection terminal *1                               | LV                |

| 26  | XI      | ĭ        | CERALOCK connection terminal *1                               | LV                |

|     |         | <u>.</u> | Digital Power Supply terminal                                 | 1                 |

| 27  | DVDD    |          | (Connect to REFA terminal outside the IC)                     | LV                |

| 28  | MODE0   | I        | Operating Mode Selection terminal                             | LV                |

| 29  | MODE1   | ĺ        | Operating Mode Selection terminal                             | LV                |

| 30  | MODE2   | ĺ        | Operating Mode Selection terminal                             | LV                |

| 31  | GAIN0   | i        | Input Sensitivity Setting terminal                            | LV                |

| 32  | GAIN1   | ĺ        | Input Sensitivity Setting terminal                            | LV                |

| 33  | NC      | _        | No Connection                                                 | -                 |

| 34  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | _                 |

| 35  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | _                 |

| 36  | PVDDML  | Power    | L-ch 12V-line VDD terminal                                    | HV                |

| 37  | PVDDML  | Power    | L-ch 12V-line VDD terminal                                    | HV                |

| 38  | OUTML   | 0        | L-ch Negative Side Output terminal                            | HV                |

| 39  | PVSSL   | GND      | L-ch 12V-line VSS terminal                                    | -                 |

| 40  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 41  | OUTPL   | 0        | L-ch Positive Side Output Terminal                            | HV                |

| 42  | PVDDPL  | Power    | L-ch 12V-line VDD terminal                                    | HV                |

| 43  | PVDDPL  | Power    | L-ch 12V-line VDD terminal                                    | HV                |

| 44  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | -                 |

| 45  | VSS     | GND      | Ground terminal (This terminal is connected to die-pad of IC) | _                 |

| 46  | NC      | -        | No Connection                                                 | -                 |

| 47  | HP      |          | Headphone Control terminal                                    | LV                |

| 48  | INL     | i        | L-ch Analog Signal Input terminal                             | LV                |

| 49  | VREFL   | Ö        | L-ch Reference Voltage terminal (with external capacitor)     | LV                |

| 50  | PVDDREG | Power    | 12V-line PVDD terminal for Regulator Circuit                  | HV                |

| 51  | REFA    | 0        | 5V Regulator Output terminal (with external capacitor)        | LV                |

| 52  | HPOL    | Ö        | L-ch Headphone Output terminal                                | LV                |

|     |         | _        | i i i i i i i i i i i i i i i i i i i                         |                   |

(Note) I: Input terminal, O: Output terminal, I/O: Input/Output terminal, O/D: Open drain output terminal

LV: Terminal for  $V_{\text{REG}}$  power supply voltage range as input voltage range.

HV: Terminal for  $V_{DDP}$  power supply voltage range as input voltage range. \*1: CERALOCK which was described above and will be described later is a registered trade mark of Murata Manufacturing Co.,Ltd.

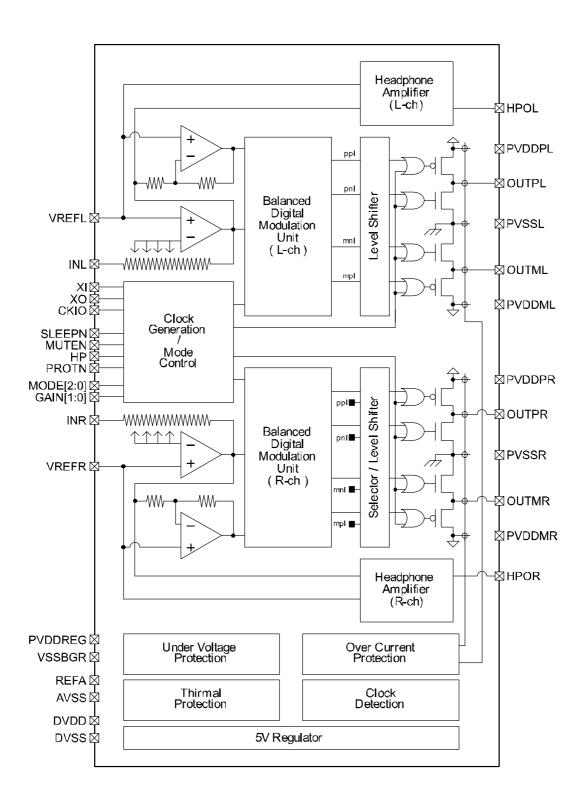

# ■Block diagram

# ■ Mode setting

#### Operating Mode

| SLEEPN | MUTEN | НР | MODE[2:0] | OUT*L | OUT*R | HPOL | HPOR | PROTN | CKIO  | Outline                           |  |

|--------|-------|----|-----------|-------|-------|------|------|-------|-------|-----------------------------------|--|

| L      | *     | *  | *         | WL    | WL    | WL   | WL   | Z     | Z     | Sleep mode                        |  |

| Н      | L     | L  | *         | WL    | WL    | WL   | WL   | Z     | -     | DA Mute mode *A)                  |  |

| Н      | L     | Н  | *         | WL    | WL    | RF   | RF   | Z     | -     | HA Mute mode *A)                  |  |

| Н      | Н     | L  | LLL       | P-H   | P-H   | WL   | WL   | Z     | -     | DA External Clock Slave mode *A)  |  |

| Н      | Н     | L  | LLH       | P-L   | P-L   | WL   | WL   | Z     | -     | DA External Clock Slave mode *A)  |  |

| Н      | Н     | L  | LHL       | P-H   | P-H   | WL   | WL   | Z     | -     | DA External Clock Master mode *A) |  |

| Н      | Н     | L  | LHH       | P-L   | P-L   | WL   | WL   | Z     | -     | DA External Clock Master mode *A) |  |

| Н      | Н     | L  | HLL       | PLS   | PLS   | WL   | WL   | Z     | -     | DA Internal Clock Slave mode *A)  |  |

| Н      | Н     | L  | HHL       | PLS   | PLS   | WL   | WL   | Z     | -     | DA Internal Clock Master mode *A) |  |

| Н      | Н     | Η  | *         | WL    | WL    | SIG  | SIG  | Z     | -     | HA mode *A)                       |  |

| Н      | *     | *  | LL*       | -     | 1     | -    | ı    | ı     | CKIN  | 4.19MHz Clock Input               |  |

| Н      | *     | *  | LH*       | -     | -     | -    | ı    | ı     | CKOUT | 4.19MHz Clock Output              |  |

| Н      | *     | *  | HLL       | -     | -     | -    | -    | -     | CKIN  | 500kHz Input (Internal Clock)     |  |

| Н      | *     | *  | HHL       | -     | -     | -    | -    | -     | CKOUT | 500kHz Output (Internal Clock)    |  |

#### Note:

- 1) "H" and "L" means logic level High and logic level Low, respectively.

- 2) "WL" means output disabled (weak pull-down output). "RF" means reference level output. "Z" means Hi-Z.

- 3) "P-H" means a carrier clock of 524kHz. "P-L" means a carrier clock of 466kHz. "PLS" means a carrier clock of approx. 500kHz (Internally generated clock).

- 4) "SIG" means an analog audio signal output.

- 5) "CKIN" means input of a clock with designated frequency. "CKOUT" means output of a designated clock.

- 6) "DA" means Digital Amplifier. "HA" means Headphone Amplifier.

- 7) Each output of OUT\*L, OUT\*R, HPOL, HPOR, PROTN, and CKIO becomes a state as shown in "Protection Mode", depending on the protection state, when entering protection state from a mode except sleep mode.

- 8) In operating modes indicated by \*A), a state of the output signal becomes a state as shown in "Protection Mode" during a protection mode.

- 9) "HLH" and "HHH" of MODE[2:0] is reserved for system use.

#### Protection Mode

|        | 2011011 |    |           |       |       |      |      |       |      |                                               |  |

|--------|---------|----|-----------|-------|-------|------|------|-------|------|-----------------------------------------------|--|

| SLEEPN | MUTEN   | ΑН | MODE[2:0] | T∗TUO | OUT*R | ПОДН | HPOR | PROTN | CKIO | Outline                                       |  |

| Н      | Н       | L  | *         | WL    | WL    | WL   | WL   | L     | Z    | Digital Amplifier Over-current Protection     |  |

| Н      | *       | *  | *         | WL    | WL    | WL   | WL   | L     | Z    | Over-Temperature Protection                   |  |

| Н      | *       | *  | *         | WL    | WL    | -    | -    | -     | -    | Clock Stop Protection                         |  |

| Н      | *       | *  | *         | WL    | WL    | WL   | WL   | Z     | Z    | Low Voltage Malfunction Prevention Protection |  |

| Н      | Н       | *  | *         | WL    | WL    | RF   | RF   | -     | -    | Power Supply Voltage Fluctuation Protection   |  |

### Note:

1) Each protection function operates when input terminal is in the designated logic condition. Output terminal becomes a state as shown in the above during protection mode.

# ■ Description of operating functions

#### Digital Amplifier Function

YDA143 has digital amplifiers with analog input, PWM pulse output, Maximum output of 15W ( $R_L$ =4 $\Omega$ ) × 2ch. Distortion of PWM pulse output signal and noise of the signal is reduced by adopting "Pure Pulse Direct Speaker Drive Circuit"

#### First Stage Amplifier Gain Setting Function

YDA143 is composed of the first stage amplifier with gain setting control and 18dB fixed-gain digital amplifier. Gain of the first stage amplifier can be set by GAIN[1:0] terminal.

Digital Amplifier Gain Setting

|          | <u> </u>       |          |                   |                       |  |  |

|----------|----------------|----------|-------------------|-----------------------|--|--|

| GAIN     | GAIN[1:0] Gain |          | Input Sensitivity | Input Impedance (RIN) |  |  |

| L L 36dB |                | 0.14Vrms | 12.1kΩ            |                       |  |  |

| L        | L H 30dB       |          | 0.28Vrms          | 22.0kΩ                |  |  |

| Н        | L              | 24dB     | 0.56Vrms          | 37.1kΩ                |  |  |

| Н        | Н              | 18dB     | 1.12Vrms          | 56.5kΩ                |  |  |

Connect a  $0.22\mu F$  or more capacitor to the audio signal input terminal (INL and INR) for the rejection of DC signal. And, half voltage of REFA terminal voltage ( $V_{REG}$ ) is output to the reference voltage terminals (VREFL and VREFR). Connect a  $1\mu F$  or more capacitor to the terminals for voltage stabilization.

#### Carrier Clock Selection Function

YDA143 can select the followings by using MODE[2:0] terminal: selection of Internal clock/External clock, selection of Master mode/Slave mode, selection of carrier clock frequency.

#### MODE[2:0] setting and each operating mode

| M | ODE[2 | :0] | Operating Mode             | CKIO terminal   | CERALOCK     | Carrier Clock Frequency |

|---|-------|-----|----------------------------|-----------------|--------------|-------------------------|

| L | L     | L   | External Clock Slave Mode  | 4.19MHz input   | Linnococcari | 524kHz                  |

| L | L     | Н   | External Clock Slave Mode  | 4.19MHZ IIIPUL  | Unnecessary  | 466kHz                  |

| L | Н     | L   | External Clock Master Mode | 4.19MHz output  | Noocoon      | 524kHz                  |

| L | Н     | Η   | External Clock Master Mode | 4. 19MHZ Output | Necessary    | 466kHz                  |

| Н | L     | L   | Internal Clock Slave Mode  | 500kHz input    | Unnecessary  | 500kHz                  |

| Н | L     | Η   | Reserved                   |                 |              |                         |

| Н | Н     | L   | Internal Clock Master Mode | 500kHz output   | Unnecessary  | 500kHz                  |

| Н | Н     | Н   | Reserved                   |                 |              |                         |

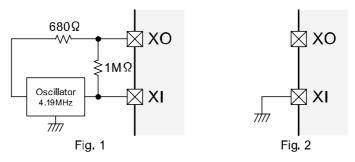

When using in External Clock Mater Mode, connect a 4.19MHz oscillator (CERALOCK) between XI and XO terminal as shown in Fig. 1. When using in other operating mode, external element to XI and XO terminal is unnecessary. At this time, XI terminal is connected to ground and XO terminal is no connection as shown in Fig. 2.

When using in multi-channel, use one YDA143 (2ch) in Master Mode and use other YDA143 in Slave Mode. At this time, connect CKIO terminal of YDA143 used in Master Mode and that of YDA143 used in Slave Mode. In addition, select the same clock (either Internal Clock or External Clock) in all YDA143.

The setting terminal for carrier clock frequency (MODE0) can be changed at any timing.

The setting terminal for clock mode (MODE2, MODE1) should be changed during power-off or sleep mode (SLEEPN=L).

#### Headphone Amplifier Function

YDA143 has class AB single-ended push-pull headphone amplifier. Headphone amplifier mode can be set by setting HP terminal to H. Audio signal input terminal and voltage reference terminal is common to digital amplifier.

Connect DC-cut capacitor to headphone amplifier output terminal (HPOL and HPOR).

When a headphone amplifier is not used, HP terminal should be "L" and output terminal (HPOL, HPOR) should be "No Connection".

#### First stage Amplifier Gain Setting function

Headphone amplifier is composed of the first stage amplifier of which gain setting is possible, and 0dB fixed-gain amplifier. Gain of the first stage amplifier can be set by GAIN[1:0] terminal.

#### Headphone Amplifier Gain Setting

| GAIN | V[1:0] | Gain | Input sensitivity | Input Impedance (RIN) |  |  |

|------|--------|------|-------------------|-----------------------|--|--|

| L    | L      | 18dB | 0.14Vrms          | 12.1kΩ                |  |  |

| L    | Н      | 12dB | 0.28Vrms          | 22.0kΩ                |  |  |

| Н    | L      | 6dB  | 0.56Vrms          | 37.1kΩ                |  |  |

| Н    | Н      | 0dB  | 1.12Vrms          | 56.5kΩ                |  |  |

#### Control Function

#### Sleep Function

When SLEEPN terminal is L, YDA143 enters the Sleep Mode.

In Sleep mode, all the circuit functions including 5V regulator are stopped to minimize the consumption current. At this time, output stages of digital amplifier and headphone amplifier are disabled and PROTN and CKIO terminal output becomes "Hi-Z".

#### **Mute Function**

When MUTEN terminal is set to L while HP terminal is L, YDA143 enters the Digital Amplifier Mute mode. In this mode, output stage of Digital Amplifier is disabled.

When MUTEN terminal is set to L while HP terminal is H, YDA143 enters the Headphone Amplifier Mute Mode. In this mode, output stage of Headphone Amplifier outputs the reference voltage.

#### **Headphone Selection Function**

When HP terminal is set to H, YDA143 enters the Headphone Amplifier mode. At this time, output stage of Digital Amplifier is disabled. On the contrary, when HP terminal is set to L, YDA143 enters Digital Amplifier mode. At this time, output of the Headphone Amplifier output is disabled.

When logic of HP terminal is changed (H to L level, or L to H level), YDA143 restarts and as the result of it, all the protection states are cleared.

#### Protection Function

YDA143 has Over-current Protection function and Clock Stop Protection function as protection functions for the digital amplifier. In addition, it has Output Current Limit function as a protection function for headphone amplifier. Moreover, YDA143 has Thermal Protection function, Low-voltage Malfunction Prevention function, and Power Supply Voltage Fluctuation Protection function commonly.

#### Over-current Protection Function

This is a function to make the Over-current Protection Mode (disables the output stage of digital amplifier in addition to the output of L signal to PROTN terminal) by detection of short-circuiting (Ground short/Power supply short/Speaker terminal short) in the output stage of digital amplifier.

The over-current protection function can be canceled by power off or setting L to SLEEPN terminal and can be automatically returned after the over-current detection by connection of PROTN terminal and SLEEPN terminal.

#### **Thermal Protection Function**

This is a function to make the Thermal Protection Mode (disables the output stage of digital amplifier and headphone amplifier in addition to the output of L signal to PROTN terminal) by detecting extraordinary high temperature of YDA143. This Thermal Protection mode can be cancelled by lowering temperature of YDA143, power off, or setting L to SLEEPN terminal and can be automatically returned after the extraordinary high temperature detection by connection of PROTN terminal and SLEEPN terminal.

#### **Clock Stop Protection Function**

This is a function to make the Clock Stop Protection mode (disables the output stage of digital amplifier) when carrier clock frequency was extraordinarily lowered in digital amplifier mode.

The Clock Stop Protection mode can be cancelled by returning carrier clock frequency to the right value.

#### Low-voltage Malfunction Prevention Function

This is a function to make the Low-voltage Protection mode (disables the output stage of digital amplifier and headphone amplifier in addition to making "Hi-Z" of PROTN terminal) when voltage at 12V-line power terminal (PVDDREG) becomes lower than Low-voltage detection threshold voltage ( $V_{UVPL}$ ) or voltage at 5V-line power terminal (REFA, DVDD) becomes lower than the voltage ( $V_{UVAL}$ ).

In addition, when voltage at 12V-line power supply terminal becomes lower than  $V_{UVPL}$ , 5V embedded regulator is also disabled.

The Low-voltage Protection mode is cancelled when voltage at each power supply terminal exceeded the low-voltage cancellation threshold voltage ( $V_{UVPH}, V_{UVAH}$ ).

#### Power Supply Voltage Detection Function

This is a function to make Mute mode when voltage at 5V Regulator output terminal (REFA) fluctuated ( $V_{MH}$ ,  $V_{ML}$ ) with respect to twice of the voltage of reference terminals (VREFL, VREFR).

#### Headphone Amplifier Output Current Limit Function

YDA143 headphone amplifier has a Current-Limit-Circuit which limits output current so as not to exceed the limit current (I<sub>OCHP</sub>).

# **YDA143**

#### ●5V Regulator Function

YDA143 outputs 5V to REFA terminal when SLEEPN terminal is H. Connect a  $1\mu F$  or more capacitor to REFA terminal for voltage stabilization.

Connect REFA terminal to DVDD terminal on a board. And, do not connect the REFA terminal to other terminals except for DVDD terminal and YDA143 control terminals.

#### ●Pop Noise Reduction Function

The Pop Noise Reduction Function works in the following cases: Power-on, Power-off, Sleep ON/OFF, Mute ON/OFF, and switching time between headphone amplifier and digital amplifier.

Pop noise at the Power-on, Power-off, and Sleep ON/OFF depends on the value of DC-cut capacitor for audio input signal. The smaller the value, the greater the effect on the pop noise reduction; however,  $0.22\mu F$  or more of capacitance is recommended in the consideration of the low frequency cutoff.

#### Correspond to Filter less

Normally, when LC filter is not used, carrier signal of 50% modulation comes into speaker even in no input signal state and causes significant loss, and as the result the speaker is heated.

Generally, 15W speaker or so is considered to have inductance component of not less than 20µH.

In the modulation method of YDA143, duty ratio of the carrier signal is several % in no input signal state, so the speaker inductance component can sufficiently inhibit speaker loss without LC filter; therefore, the speaker is not heated.

#### Speaker Inductance

When YDA143 is used without LC filter, speaker inductance component reduces speaker loss in the MUTE state; therefore, use a speaker with inductance component of 20µH or more at the carrier clock frequency.

#### ●LC Filter

When connecting LC filters to YDA143, make the following LC filter circuit. Use the following constant in accordance with speaker impedance. By using the following constant, low-pass filter with cutoff frequency=50kHz or so, Q=0.7 or so is configured.

#### LC Filter Constant

| RL | L1            | C1       | C2              |

|----|---------------|----------|-----------------|

| 4Ω | 10 <i>μ</i> H | 0.47 μ F | 0.01 <i>μ</i> F |

| 6Ω | 15 <i>μ</i> Η | 0.39 μ F | 0.01 <i>μ</i> F |

| 8Ω | 22 μ H        | 0.22 μ F | 0.01 <i>μ</i> F |

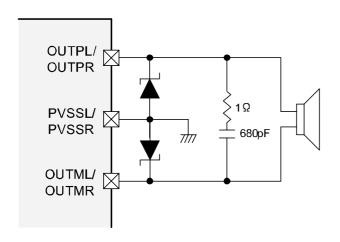

#### Schottky-diode and snubber circuit

YDA143 should connect Schottky-diode and snubber circuit with the output terminal to prevent IC destruction when the output is short-circuited.

Schottky-diode is connected between each output terminal and PVSS.

The snubber circuit is connected between positive side output terminal and negative side output terminal.

### Recommended parts

Schottky-diode: ROHM, RB160M-30

Forward current surge peak = 30A or more, Average forward current = 1A or more,

Forward voltage ( $I_F=1A$ ) = 0.43V or less

Snubber circuit: R=1Ω, C=680pF

Schottky-diode and snubber circuit

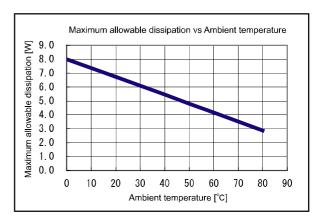

#### Allowable Dissipation

The power dissipation of YDA143 is limited by the junction temperature rating (125°C) and package thermal resistance (15.6°C/W).

The power dissipation and junction temperature of YDA143 can be found by the following formula. For the use of YDA143, take care not to exceed the power dissipation and junction temperature.

#### •Formula for the Power Dissipation

Ploss = (Pout \* Rpn / RI) \* 2 + Idc \* Vdc

Ploss : Allowable Dissipation (W)

Pout : Output Power (W) Rpn : 0.39 (Constant) RI : Load Resistor ( $\Omega$ )

Idc  $: 0.040(Constant / at V_{DDP}=12V)$

0.030(Constant / at  $V_{DDP}$ =9V)

0.045(Constant / at  $V_{DDP}$ =13.5V)

Vdc : Power supply voltage (V)

Maximum allowable dissipation of YDA143

#### ·Formula for the junction temperature

Tj = Ploss \*

$$\theta$$

ja + Ta

Ploss : Allowable Dissipation (W)

θja :15.6 (Constant/ package thermal resistance (°C/W))

Ta : Ambient Temperature (°C)

#### Package Thermal Resistance

The package (52SSOP) for YDA143 has a Thermal Pad for radiation on the surface. Use this Thermal Pad by soldering on a board.

The package's thermal resistance is  $15.6^{\circ}\text{C/W}$  (4-layer board). This thermal resistance is a value measured under the following conditions: board size  $136\text{mm} \times 85\text{mm}$ , 1st layer and 4th layer copper foil board density 154%, 2nd layer and 3rd layer copper foil board density 200%, no wind. In addition, the lower side pattern of the Thermal Pad is connected to all the layers in a board by through holes ( $\varphi 0.4$ ).

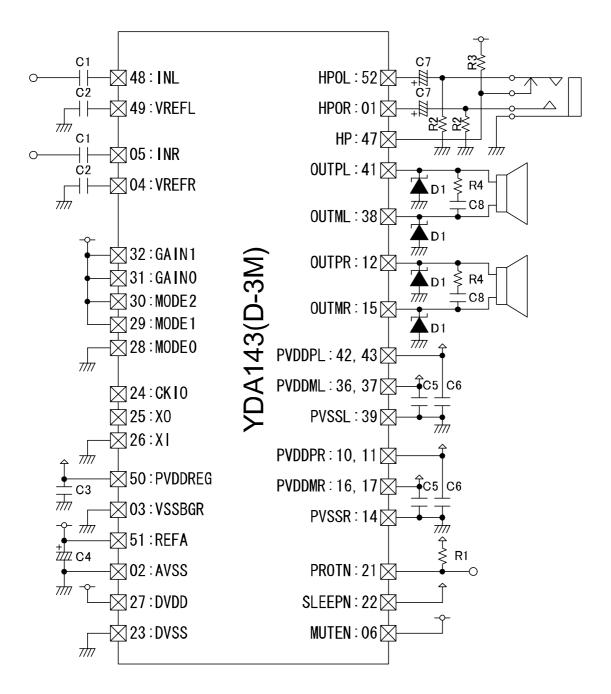

# ■Application circuit examples

●2-channel Operating Mode (Internal Clock Master Mode)

| ID    | Value    | Element                      | ID | Value                     | Element       |  |

|-------|----------|------------------------------|----|---------------------------|---------------|--|

| C1    | 0.22 μ F | Multilayer ceramic capacitor | R1 | 100kΩ                     | Chip Resistor |  |

| C2    | 10 μ F   | Multilayer ceramic capacitor | R2 | 1kΩ                       | Chip Resistor |  |

| C3    | 0.1 μ F  | Multilayer ceramic capacitor | R3 | 100kΩ                     | Chip Resistor |  |

| C4    | 100 μ F  | Electrolytic capacitor       | R4 | 1Ω                        | Chip Resistor |  |

|       |          | (0.1 μ F Ceramic capacitor)  | R5 | 680Ω                      | Chip Resistor |  |

| C5,C6 | 4.7 μ F  | Multilayer ceramic capacitor | R6 | 1ΜΩ                       | Chip Resistor |  |

| C7    | 330 μ F  | Electrolytic capacitor       | U1 | CERALOCK: CSTCR4M19G53-B0 |               |  |

| C8    | 680pF    | Multilayer ceramic capacitor | D1 | Schottky-diode: RB160M-30 |               |  |

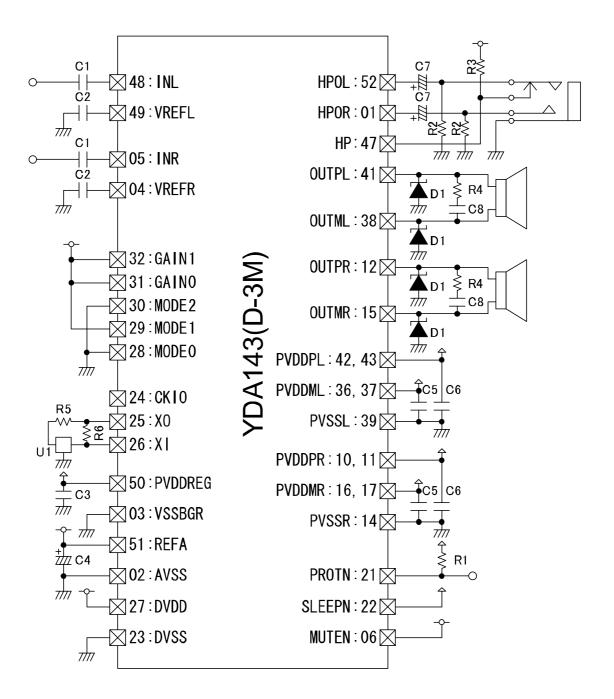

●2-channel Operating Mode (External Clock Master Mode)

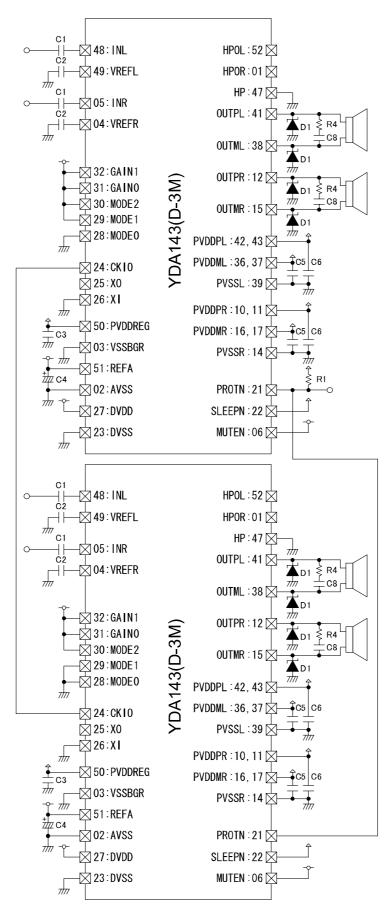

• Multi-channel Operating Mode (Internal Clock Master Mode/Slave Mode)

# ■Electrical characteristic

# ● Absolute Maximum Ratings Note 6)

| Item                                                      | Symbol           | Min.                 | Max.                  | Unit |

|-----------------------------------------------------------|------------------|----------------------|-----------------------|------|

| Voltage Range of Power supply terminal (VDDP) Note 1,2,3) | $V_{DDP}$        | -0.3                 | 14.0                  | V    |

| Voltage Range of SLEEPN, PROTN terminal                   | $V_{IN1}$        | V <sub>SS</sub> -0.3 | V <sub>DDP</sub> +0.3 | V    |

| Voltage Range of CKIO Input/Output terminal               | V <sub>IN2</sub> | V <sub>SS</sub> -0.3 | V <sub>REG</sub> +1.0 | V    |

| Voltage Range of terminals for control Note 4)            | V <sub>IN3</sub> | V <sub>SS</sub> -0.3 | V <sub>REG</sub> +1.0 | V    |

| Voltage Range of Input/output terminals Note 5)           | $V_{IN4}$        | V <sub>SS</sub> -0.3 | V <sub>REG</sub> +0.3 | V    |

| Allowable dissipation (Ta=25°C)                           | P <sub>D25</sub> |                      | 6.4                   | W    |

| Allowable dissipation (Ta=70°C)                           | P <sub>D70</sub> |                      | 3.5                   | W    |

| Junction temperature                                      | $T_{JMAX}$       |                      | 125                   | °C   |

| Storage temperature                                       | T <sub>STG</sub> | -50                  | 125                   | ٥    |

- Note 1) VSS means AVSS, VSSBGR, DVSS, PVSSR, PVSSL and VSS. Place all VSS terminals in the same potential.

- Note 2) All the voltages are measured with respect to  $V_{\rm SS}$ =0V.

- Note 3) Power supply terminal (VDDP) means PVDDREG, PVDDPR, PVDDMR, PVDDPL and PVDDML.

- Note 4) Control Input/Output terminal means MUTEN, HP, GAIN[1:0] and MODE[2:0].

- Note 5) Input/output terminal means INL, VREFL, INR, VREFR, XI and XO.

- Note 6) Absolute Maximum Ratings is values which must not be exceeded to guarantee device reliability and life, and when using a device in excess even a moment, it may immediately cause damage to device or may significantly deteriorate its reliability

#### Recommended Operating Condition

| Item                          | Symbol    | Min. | Тур. | Max. | Unit |

|-------------------------------|-----------|------|------|------|------|

| Power Supply Voltage Note 7)  | $V_{DDP}$ | 9.0  | 12.0 | 13.5 | V    |

| Operating Ambient Temperature | Ta        | -40  | 25   | 85   | °C   |

| Speaker Impedance             | $R_{LS}$  | 3.75 | 4    |      | Ω    |

| Headphone Impedance           | $R_{LHP}$ | 16   | 32   |      | Ω    |

Note 7) All the voltages are measured with respect to  $V_{SS}=0V$ .

# ●DC Characteristics (V<sub>SS</sub>=0V, V<sub>DDP</sub>=12V±0.5V, Ta=0°C to 85°C, unless otherwise specified)

| Item                                                             | Symbol            | Min. | Тур.     | Max. | Unit |

|------------------------------------------------------------------|-------------------|------|----------|------|------|

| REFA Output terminal voltage                                     | $V_{REG}$         | 4.5  | 5        | 5.5  | V    |

| PROTN terminal Low level output voltage (I <sub>OL</sub> =1.6mA) | $V_{OLP}$         |      |          | 0.4  | V    |

| CKIO terminal High level output voltage (I <sub>OH</sub> =-80μA) | V <sub>OHC</sub>  | 4.0  |          |      | V    |

| CKIO terminal Low level output voltage (I <sub>OL</sub> =1.6mA)  | $V_{OLC}$         |      |          | 0.5  | V    |

| SLEEPN, CKIO terminal High level input voltage                   | V <sub>IH1</sub>  | 2.2  |          |      | V    |

| SLEEPN, CKIO terminal Low level input voltage                    | $V_{IL1}$         |      |          | 8.0  | V    |

| Input terminals for control High level input voltage             | $V_{IH2}$         | 3.5  |          |      | V    |

| Input terminals for control Low level input voltage              | $V_{IL2}$         |      |          | 1.5  | V    |

| REFA, DVDD terminal Start-up threshold voltage                   | $V_{UVAH}$        |      | 3.7      |      | V    |

| REFA, DVDD terminal Cutoff threshold voltage                     | $V_{UVAL}$        |      | 3.3      |      | V    |

| PVDDREG terminal start-up threshold voltage                      | $V_{UVPH}$        |      | 8.0      |      | V    |

| PVDDREG terminal Cutoff threshold voltage                        | $V_{UVPL}$        |      | 7.6      |      | V    |

| Power Supply Fluctuation Cutoff threshold voltage (lower limit)  | $V_{ML}$          |      | VREF*1.8 |      | V    |

| Power Supply Fluctuation Cutoff threshold voltage (upper limit)  | $V_{MH}$          |      | VREF*2.2 |      | V    |

| Headphone Amplifier limit current                                | I <sub>OCHP</sub> |      | 50       |      | mA   |

# ●AC characteristics (V<sub>SS</sub>=0V, V<sub>DDP</sub>=12V±0.5V, Ta=0°C to 85°C, unless otherwise specified)

| Item                                                              | Symbol             | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------|--------------------|------|------|------|------|

| Master Clock Frequency (Internal clock mode)                      | F <sub>CK</sub>    |      | 500  |      | kHz  |

| Clock Stop Detection Carrier Clock Frequency                      | F <sub>UFP</sub>   |      | 150  |      | kHz  |

| Consumption Current (Sleep mode)                                  | I <sub>SLEEP</sub> |      | 1    |      | μA   |

| Consumption Current (Mute mode)                                   | I <sub>MUTE</sub>  |      | 20   |      | mA   |

| Consumption Current (Digital amplifier output in no-signal input) | I <sub>DDD</sub>   |      | 40   |      | mA   |

| Consumption Current (Headphone output in no-signal input)         |                    |      | 10   |      | mA   |

Note 1)  $4\Omega$  resistor and  $30\mu$ H coil are used as an output load in order to obtain various digital amplifier characteristics.

● Analog Characteristics (V<sub>SS</sub>=0V, V<sub>DDP</sub>=12V, Ta=25°C, Frequency:1kHz, unless otherwise specified)

# **Digital Amplifier Section**

| Item                                        | Condition                             | Symbol  | Min. | Тур. | Max. | Unit |

|---------------------------------------------|---------------------------------------|---------|------|------|------|------|

| Maximum Output (THD+N=10%)                  | $R_L=4\Omega$                         | Po      |      | 15.0 |      | W    |

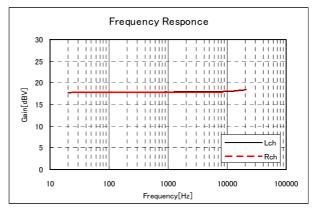

| Voltage Gain (at 1V input sensitivity)      |                                       | $A_{V}$ |      | 18   |      | dB   |

| Total Harmonic Distortion Rate (BW: 20kHz)  | $R_L=4\Omega$ , $P_O=1.5W$            | THD+N   |      | 0.04 |      | %    |

| Signal /Noise Ratio<br>(BW: 20kHz A-Filter) | $R_L=4\Omega, P_O=15W,$ GAIN[1:0]=H,H | SNR     |      | 103  |      | dB   |

| Channel Separation Ratio                    | GAIN[1:0]=H,H                         | CS      |      | -65  |      | dB   |

| Maximum Efficiency                          | $R_L=4\Omega$ , $P_O=15W$             | η       |      | 87   |      | %    |

| Output Offset Voltage                       |                                       | Vo      |      | ±20  |      | mV   |

Note) All the values of analog characteristics were obtained by using our evaluation circumstance.

Depending upon parts and pattern layout to use, characteristics may be changed.

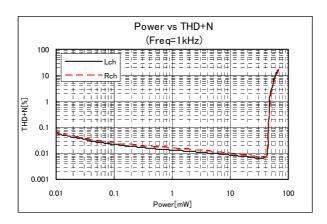

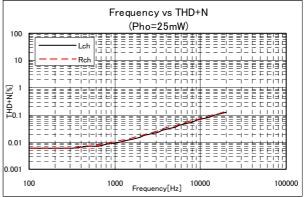

#### Headphone Amplifier Section

| Item                                        | Condition                                          | Symbol          | Min. | Тур. | Max. | Unit |

|---------------------------------------------|----------------------------------------------------|-----------------|------|------|------|------|

| Maximum Output (THD+N=10%)                  | R <sub>L</sub> =32Ω                                | P <sub>ho</sub> |      | 50.0 |      | mW   |

| Total Harmonic Distortion Rate (BW: 20kHz)  | $R_L$ =32 $\Omega$ , $P_{ho}$ =25mW                | THD+N           |      | 0.01 |      | %    |

| Signal /Noise Ratio<br>(BW: 20kHz A-Filter) | $R_L$ =32 $\Omega$ , $P_{ho}$ =50mW, GAIN[1:0]=H,H | SNR             |      | 95   |      | dB   |

| Channel Separation Ratio                    | GAIN[1:0]=H,H                                      | CS              |      | -75  |      | dB   |

$<sup>4\</sup>Omega$  resistor and  $30\mu H$  coil are used as an output load in order to obtain various digital amplifier characteristics.

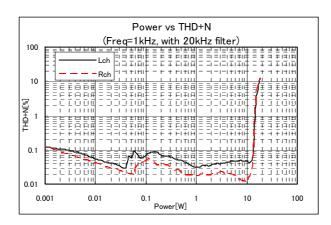

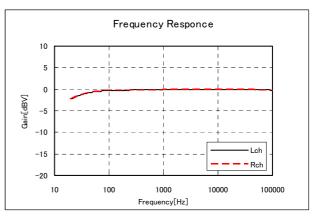

# ■Typical characteristics examples

● Digital Amplifier Characteristics (V<sub>DDP</sub>=12V, R<sub>L</sub>=4Ω+30μH, Frequency=1kHz, GAIN[1:0]=H,H, MODE[2:0]=L,H,L, unless otherwise specified)

• Headphone Amplifier Characteristics (V<sub>DDP</sub>=12V, R<sub>L</sub>=32Ω, Frequency=1kHz, GAIN[1:0]=H,H, MODE[2:0]=L,H,L, unless otherwise specified)

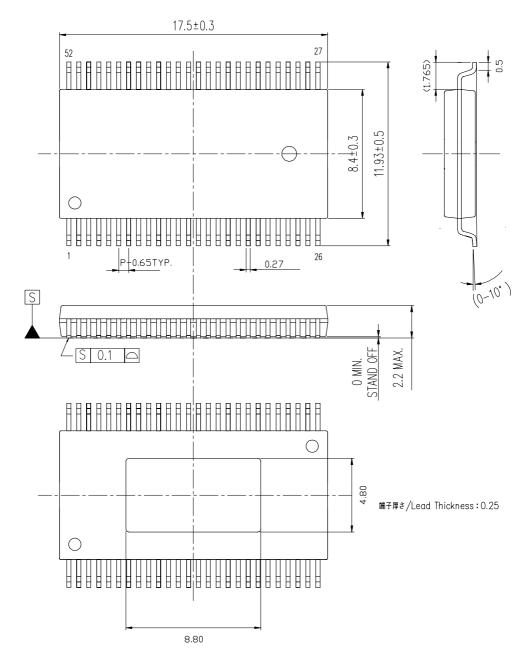

# ■Package outline

C-PK52EP-1

モールドコーナー形状は、この図面と若干異なるタイプもあります。 カッコ内の寸法値は参考値です。

モールド外形寸法はバリを含みません。

単位: mm

The shape of the molded corner may slightly differ from the shape in this diagram.

The figure in the parentheses () should be used as a reference.

Plastic body dimensions do not include resin burr.

UNIT: mm

注) 表面実装LSIは、保管条件、及び半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせください。

Note: The storage and soldering of LSIs for surface mounting need special consideration. For detailed information, please contact your local Yamaha agent.

**YDA143**

MEMO

# IMPORTANT NOTICE

- YAMAHA RESERVES THE RIGHT TO MAKE CHANGES TO ITS PRODUCTS AND TO THIS DOCUMENT WITHOUT NOTICE. THE INFORMATION CONTAINED IN THIS DOCUMENT HAS BEEN CAREFULLY CHECKED AND IS BELIEVED. HOWEVER, YAMAHA SHALL ASSUME NO RESPONSIBILITIES FOR INACCURACIES AND MAKE NO COMMITMENT TO UPDATE OR TO KEEP CURRENT THE INFORMATION CONTAINED IN THIS DOCUMENT.

- 2. THESE YAMAHA PRODUCTS ARE DESIGNED ONLY FOR COMMERCIAL AND NORMAL INDUSTRIAL APPLICATIONS, AND ARE NOT SUITABLE FOR OTHER USES, SUCH AS MEDICAL LIFE SUPPORT EQUIPMENT, NUCLEAR FACILITIES, CRITICAL CARE EQUIPMENT OR ANY OTHER APPLICATION THE FAILURE OF WHICH COULD LEAD TO DEATH, PERSONAL INJURY OR ENVIRONMENTAL OR PROPERTY DAMAGE. USE OF THE PRODUCTS IN ANY SUCH APPLICATION IS AT THE CUSTOMER'S OWN RISK AND EXPENSE.

- YAMAHA SHALL ASSUME NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCT.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF PRODUCTS. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMES OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

- 6. YAMAHA MAKES EVERY EFFORT TO IMPROVE THE QUALITY AND RELIABILITY OF ITS PRODUCTS. HOWEVER, ALL SEMICONDUCTOR PRODUCTS FAIL WITH SOME PROBABILITY. THEREFORE, YAMAHA REQUIRES THAT SUFFICIENT CARE BE GIVEN TO ENSURING SAFE DESIGN IN CUSTOMER PRODUCTS SUCH AS REDUNDANT DESIGN, ANTI-CONFLAGRATION DESIGN, AND DESIGN FOR PREVENTING MALFUNCTION IN ORDER TO PREVENT ACCIDENTS RESULTING IN INJURY OR DEATH, FIRE OR OTHER SOCIAL DAMAGE FROM OCCURRING AS A RESULT OF PRODUCT FAILURE.

- 7. INFORMATION DESCRIBED IN THIS DOCUMENT: APPLICATION CIRCUITS AND ITS CONSTANTS AND CALCULATION FORMULAS, PROGRAMS AND CONTROL PROCEDURES ARE PROVIDED FOR THE PURPOSE OF EXPLAINING TYPICAL OPERATION AND USAGE. THEREFORE, PLEASE EVALUATE THE DESIGN SUFFICIENTLY AS WHOLE SYSTEM UNDER THE CONSIDERATION OF VARIOUS EXTERNAL OR ENVIRONMENTAL CONDITIONS AND DETERMINE THEIR APPLICATION AT THE CUSTOMER'S OWN RISK. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR CLAIMS, DAMAGES, COSTS AND EXPENSES CAUSED BY THE CUSTOMER OR ANY THIRD PARTY, OWING TO THE USE OF THE ABOVE INFORMATION.

**Notice**

The specifications of this product are subject to improvement changes without prior notice.

AGENT —

# - YAMAHA CORPORATION -

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Iwata,

Shizuoka, 438-0192, Japan

Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku, Tokyo, 108-8568, Japan

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office 3-12-12, Minami Senba, Chuo-ku, Osaka City, Osaka, 542-0081, Japan

Tel. +81-6-6252-6221 Fax. +81-6-6252-6229