## ISL12082

I<sup>2</sup>C-Bus™ Real Time Clock with Two Interrupts, Alarm, and Timer

Data Sheet

November 24, 2008

<u>FN67</u>31.3

# Low Power RTC with Battery ReSeal<sup>™</sup>, 2 IRQs, Hundredths of a Second Time, and Crystal Compensation

intercil

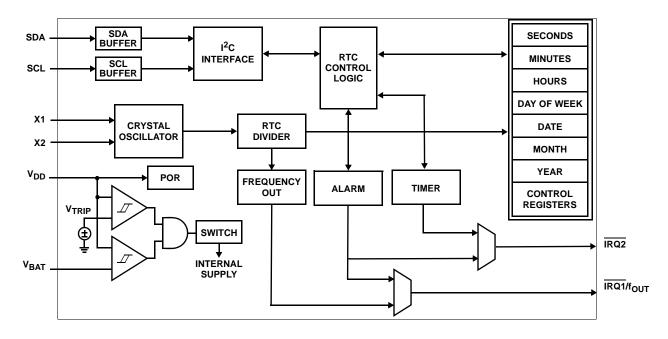

The ISL12082 device is a low power real time clock with timing and crystal compensation, clock/calendar, power fail indicator, 2 IRQs, periodic or polled alarm, timer/watchdog, and intelligent battery backup switching.

The oscillator uses an external, low-cost 32.768kHz crystal. The real time clock tracks time with separate registers for hours, minutes, seconds and hundredths of a second. The device has calendar registers for date, month, year and day of the week. The calendar is accurate through 2099, with automatic leap year correction.

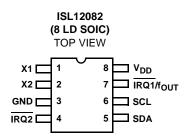

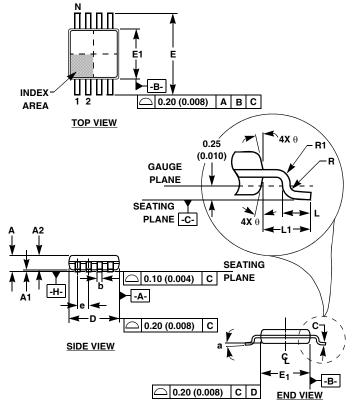

### **Pinouts**

#### Features

- Real Time Clock/Calendar

- Tracks Time in Hours, Minutes, Seconds, and Hundredths of a Second

- Day of the Week, Day, Month, and Year

- 4 Selectable Frequency Outputs

- Alarm

- Settable to the Second, Minute, Hour, Day of the Week, Day, or Month

- Single Event or Pulse Interrupt Mode

- Timer

- 4 Selectable Timer Functions

- 4 Selectable Timer Clock Frequencies

- Single Event or Pulse Interrupt Mode

- · Automatic Backup to Battery or Supercapacitor

- Power Failure Detection

- Battery ReSeal<sup>™</sup>

- On-Chip Oscillator Compensation

- I<sup>2</sup>C Interface

- 400kHz Data Transfer Rate

- 800nA Battery Supply Current

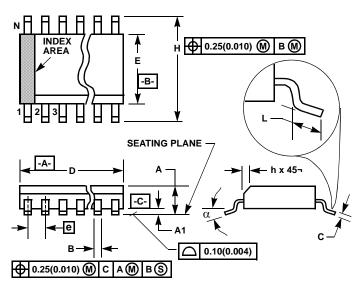

- Small Package Options

- 8 Ld SOIC Package

- 10 Ld MSOP Package

- Pb-Free (RoHS Compliant)

#### Applications

- Utility Meters

- HVAC Equipment

- Audio/Video Components

- Set-Top Box/Television

- Modems

- Network Routers, Hubs, Switches, Bridges

- · Cellular Infrastructure Equipment

- Fixed Broadband Wireless Equipment

- Pagers/PDA

- POS Equipment

- Test Meters/Fixtures

- Office Automation (Copiers, Fax)

- Home Appliances

- Computer Products

## Ordering Information

| PART NUMBER<br>(Note) | PART<br>MARKING | V <sub>DD</sub> RANGE<br>(V) | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)          | PKG.<br>DWG. # |

|-----------------------|-----------------|------------------------------|---------------------|-------------------------------|----------------|

| SL12082IB8Z           | 12082 IBZ       | 2.7 to 5.5                   | -40 to +85          | 8 Ld SOIC                     | M8.15          |

| ISL12082IB8Z-T*       | 12082 IBZ       | 2.7 to 5.5                   | -40 to +85          | 8 Ld SOIC<br>(Tape and Reel)  | M8.15          |

| ISL12082IUZ           | 12082           | 2.7 to 5.5                   | -40 to +85          | 10 Ld MSOP                    | M10.118        |

| ISL12082IUZ-T*        | 12082           | 2.7 to 5.5                   | -40 to +85          | 10 Ld MSOP<br>(Tape and Reel) | M10.118        |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matter tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## Block Diagram

## **Pin Descriptions**

| -                | PIN<br>NUMBER |                       |                                                                                                                                                                                                       |  |  |  |  |

|------------------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SOIC MSOP SYMBOL |               | SYMBOL                | DESCRIPTION                                                                                                                                                                                           |  |  |  |  |

| 1                | 1             | X1                    | The X1 pin is the input of an inverting amplifier and is intended to be connected to one pin of an external 32.768kHz quartz crystal. X1 can also be driven directly from a 32.768kHz source.         |  |  |  |  |

| 2                | 2             | X2                    | The X2 pin is the output of an inverting amplifier and is intended to be connected to one pin of an external 32.768kHz quartz crystal.                                                                |  |  |  |  |

| -                | 3             | V <sub>BAT</sub>      | This input provides a backup supply voltage to the device. $V_{BAT}$ supplies power to the device in the event that the $V_{DD}$ supply fails. This pin should be tied to ground if not used.         |  |  |  |  |

| 3                | 4             | GND                   | Ground                                                                                                                                                                                                |  |  |  |  |

| -                | 5             | NC                    | No Connect                                                                                                                                                                                            |  |  |  |  |

| 4                | 6             | IRQ2                  | Interrupt Output 2 is a multi-functional pin that can be used as alarm interrupt or timer interrupt pin. The function is set via the configuration register.                                          |  |  |  |  |

| 5                | 7             | SDA                   | Serial Data (SDA) is a bi-directional pin used to transfer serial data into and out of the device. It has an open drain output and may be wire OR'ed with other open drain or open collector outputs. |  |  |  |  |

| 6                | 8             | SCL                   | The Serial Clock (SCL) input is used to clock all serial data into and out of the device.                                                                                                             |  |  |  |  |

| 7                | 9             | IRQ1/f <sub>OUT</sub> | Interrupt Output 1/Frequency Output is a multi-functional pin that can be used as alarm interrupt or frequency output pin. The function is set via the configuration register.                        |  |  |  |  |

| 8                | 10            | V <sub>DD</sub>       | Power supply                                                                                                                                                                                          |  |  |  |  |

#### **Absolute Maximum Ratings**

Voltage on V<sub>DD</sub>, V<sub>BAT</sub>, SCL, SDA, IRQ1/f<sub>OUT</sub> and IRQ2 Pins

(respect to GND) ......-0.5V to 6.5V Voltage on X1 and X2 Pins

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| 8 Ld SOIC                                        | 120                    |

| 10 Ld MSOP                                       | 152                    |

| Maximum Storage Temperature Range65°             | C to +150°C            |

| Pb-Free Reflow Profile                           | e link below           |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

DC Operating Characteristics - RTC Temperature = -40°C to +85°C, unless otherwise stated.

| SYMBOL                    | PARAMETER                                   | CONDITIONS                                    | MIN<br>(Note 6) | TYP<br>(Note 5) | MAX<br>(Note 6) | UNITS | NOTES |

|---------------------------|---------------------------------------------|-----------------------------------------------|-----------------|-----------------|-----------------|-------|-------|

| V <sub>DD</sub>           | Main Power Supply                           |                                               | 2.7             |                 | 5.5             | V     |       |

| VBAT                      | Battery Supply Voltage                      |                                               | 1.8             |                 | 5.5             | V     |       |

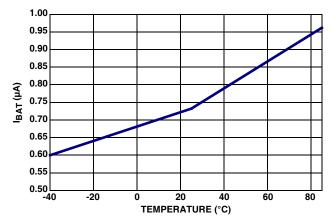

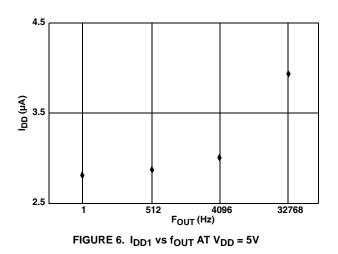

| I <sub>DD1</sub>          | Supply Current                              | $V_{DD} = 5V$                                 |                 | 2.8             | 6               | μA    | 2, 3  |

|                           |                                             | $V_{DD} = 3V$                                 |                 | 1.6             | 4               | μA    |       |

| I <sub>DD2</sub>          | Supply Current With I <sup>2</sup> C Active | V <sub>DD</sub> = 5V                          |                 | 40              | 120             | μA    | 2, 3  |

| I <sub>DD3</sub>          | Supply Current (Low Power Mode)             | $V_{DD} = 5V$ , LPMODE = 1                    |                 | 2.3             | 5               | μA    | 2     |

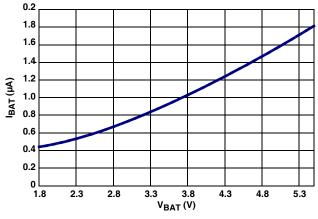

| IBAT                      | Battery Supply Current                      | V <sub>BAT</sub> = 3V, +25°C                  |                 | 800             | 950             | nA    | 2, 9  |

| ILI                       | Input Leakage Current on SCL                |                                               | -1              | 0.1             | +1              | μA    |       |

| ILO                       | I/O Leakage Current on SDA                  |                                               | -1              | 0.1             | +1              | μA    |       |

| V <sub>TRIP</sub>         | VBAT Mode Threshold                         |                                               | 1.8             | 2.15            | 2.4             | V     | 9     |

| VTRIPHYS                  | V <sub>TRIP</sub> Hysteresis                |                                               |                 | 36              |                 | mV    | 7, 9  |

| VBATHYS                   | V <sub>BAT</sub> Hysteresis                 |                                               |                 | 53              |                 | mV    | 7, 9  |

| IRQ1/f <sub>OUT</sub> and | RQ2                                         |                                               | ł               |                 | 1               |       |       |

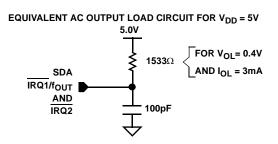

| V <sub>OL</sub>           | Output Low Voltage                          | V <sub>DD</sub> = 5V<br>I <sub>OL</sub> = 3mA |                 | 0.02            | 0.4             | V     |       |

|                           |                                             | $V_{DD} = 2.7V$<br>$I_{OL} = 1mA$             |                 | 0.02            | 0.4             | V     |       |

**Power-Down Timing**

Timing Temperature = -40°C to +85°C, unless otherwise stated.

| SYMBOL              | PARAMETER                         | CONDITIONS | MIN<br>(Note 6) | TYP<br>(Note 5) | MAX<br>(Note 6) | UNITS | NOTES |

|---------------------|-----------------------------------|------------|-----------------|-----------------|-----------------|-------|-------|

| V <sub>DD SR-</sub> | V <sub>DD</sub> Negative Slewrate |            |                 |                 | 5               | V/ms  | 4, 9  |

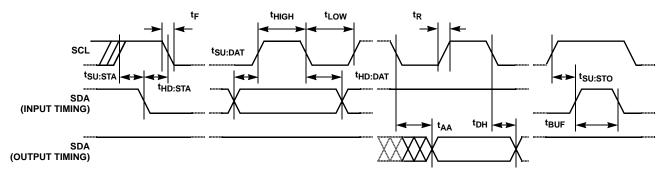

Serial Interface Specifications Over the recommended operating conditions, unless otherwise specified.

| SYMBOL          | PARAMETER                                     | TEST CONDITIONS | MIN<br>(Note 6)          | TYP<br>(Note 5)           | MAX<br>(Note 6)          | UNITS | NOTES |

|-----------------|-----------------------------------------------|-----------------|--------------------------|---------------------------|--------------------------|-------|-------|

| VIL             | SDA and SCL Input Buffer LOW Voltage          |                 | -0.3                     |                           | 0.3 x<br>V <sub>DD</sub> | V     |       |

| V <sub>IH</sub> | SDA and SCL Input Buffer HIGH<br>Voltage      |                 | 0.7 x<br>V <sub>DD</sub> |                           | V <sub>DD</sub> +<br>0.3 | V     |       |

| Hysteresis      | SDA and SCL Input Buffer<br>Hysteresis        |                 |                          | 0.05 x<br>V <sub>DD</sub> |                          | V     | 7, 8  |

| V <sub>OL</sub> | SDA Output Buffer LOW Voltage,<br>Sinking 3mA |                 | 0                        | 0.02                      | 0.4                      | V     |       |

### ISL12082

| SYMBOL                                           | PARAMETER                                                           | TEST CONDITIONS                                                                                                                                                   | MIN<br>(Note 6)  | TYP<br>(Note 5) | MAX<br>(Note 6) | UNITS | NOTES |

|--------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------|-------|-------|

| Cpin                                             | SDA and SCL Pin Capacitance                                         | $T_{A} = +25^{\circ}C, f = 1MHz, V_{DD} = 5V, V_{IN} = 0V, V_{OUT} = 0V$                                                                                          |                  |                 | 10              | pF    | 7, 8  |

| f <sub>SCL</sub>                                 | SCL Frequency                                                       |                                                                                                                                                                   |                  |                 | 400             | kHz   |       |

| t <sub>IN</sub>                                  | Pulse Width Suppression Time at SDA and SCL Inputs                  | Any pulse narrower than the max spec is suppressed                                                                                                                |                  |                 | 50              | ns    |       |

| t <sub>AA</sub>                                  | SCL Falling Edge to SDA Output<br>Data Valid                        | SCL falling edge crossing 30% of $V_{DD},$ until SDA exits the 30% to 70% of $V_{DD}$ window                                                                      |                  |                 | 900             | ns    |       |

| <sup>t</sup> BUF                                 | Time the Bus Must Be Free Before<br>the Start of a New Transmission | SDA crossing 70% of $V_{DD}$ during a STOP condition, to SDA crossing 70% of $V_{DD}$ during the following START condition                                        | 1300             |                 |                 | ns    |       |

| <sup>t</sup> LOW                                 | Clock LOW Time                                                      | Measured at the 30% of $V_{DD}$ crossing                                                                                                                          | 1300             |                 |                 | ns    |       |

| <sup>t</sup> HIGH                                | Clock HIGH Time                                                     | Measured at the 70% of $V_{DD}$ crossing                                                                                                                          | 600              |                 |                 | ns    |       |

| <sup>t</sup> SU:STA                              | START Condition Setup Time                                          | SCL rising edge to SDA falling edge. Both crossing 70% of $\mathrm{V}_{\mathrm{DD}}$                                                                              | 600              |                 |                 | ns    |       |

| <sup>t</sup> HD:STA                              | START Condition Hold Time                                           | From SDA falling edge crossing 30% of $\rm V_{DD}$ to SCL falling edge crossing 70% of $\rm V_{DD}$                                                               | 600              |                 |                 | ns    |       |

| <sup>t</sup> SU:DAT                              | Input Data Setup Time                                               | From SDA exiting the 30% to 70% of $V_{DD}$ window, to SCL rising edge crossing 30% of $V_{DD}$                                                                   | 100              |                 |                 | ns    |       |

| <sup>t</sup> HD:DAT                              | Input Data Hold Time                                                | From SCL falling edge crossing 30% of $\rm V_{DD}$ to SDA entering the 30% to 70% of $\rm V_{DD}$ window                                                          | 0                |                 | 900             | ns    |       |

| t <sub>SU:STO</sub>                              | STOP Condition Setup Time                                           | From SCL rising edge crossing 70% of $\rm V_{DD},$ to SDA rising edge crossing 30% of $\rm V_{DD}$                                                                | 600              |                 |                 | ns    |       |

| <sup>t</sup> HD:STO                              | STOP Condition Hold Time                                            | From SDA rising edge to SCL falling edge<br>Both crossing 70% of V <sub>DD</sub>                                                                                  | 600              |                 |                 | ns    |       |

| <sup>t</sup> DH                                  | Output Data Hold Time                                               | From SCL falling edge crossing 30% of $V_{DD},$ until SDA enters the 30% to 70% of $V_{DD}$ window                                                                | 0                |                 |                 | ns    |       |

| t <sub>R</sub>                                   | SDA and SCL Rise Time                                               | From 30% to 70% of V <sub>DD</sub>                                                                                                                                | 20 +<br>0.1 x Cb |                 | 300             | ns    | 7, 8  |

| t <sub>F</sub>                                   | SDA and SCL Fall Time                                               | II Time From 70% to 30% of V <sub>DD</sub> 0.                                                                                                                     |                  |                 | 300             | ns    | 7, 8  |

| Cb                                               | Capacitive Loading of SDA or SCL                                    | Total on-chip and off-chip                                                                                                                                        | 10               |                 | 400             | pF    | 7, 8  |

| Rpu SDA and SCL Bus Pull-Up<br>Resistor Off-Chip |                                                                     | Maximum is determined by $t_R$ and $t_F$<br>For Cb = 400pF, max is about $2k\Omega$ to ~2.5k $\Omega$<br>For Cb = 40pF, max is about $15k\Omega$ to ~20k $\Omega$ | 1                |                 |                 | kΩ    | 7, 8  |

#### Serial Interface Specifications Over the recommended operating conditions, unless otherwise specified. (Continued)

NOTES:

- 2.  $\overline{\text{IRQ}}$  and  $f_{\text{OUT}}$  Inactive.

- 3. LPMODE = 0 (default).

- 4. In order to ensure proper timekeeping, the  $V_{\mbox{DD}\mbox{SR-}}$  specification must be followed.

- 5. Typical values are for T = +25°C and 3.3V supply voltage.

- 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- $\ensuremath{\mathsf{7.}}$  Limits should be considered typical and are not production tested.

- These are I<sup>2</sup>C specific parameters and are not tested, however, they are used to set conditions for testing devices to validate specification.

- 9. Parameters are for 10 Ld MSOP package only.

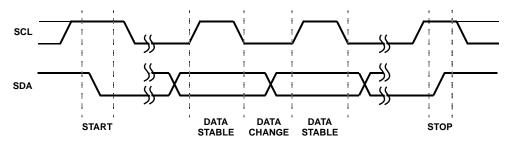

## SDA vs SCL Timing

## Symbol Table

| WAVEFORM | INPUTS                            | OUTPUTS                            |

|----------|-----------------------------------|------------------------------------|

|          | Must be steady                    | Will be steady                     |

|          | May change<br>from LOW<br>to HIGH | Will change<br>from LOW<br>to HIGH |

|          | May change<br>from HIGH<br>to LOW | Will change<br>from HIGH<br>to LOW |

|          | Don,ÄöÐÑĐ¥t<br>Changes Allowed    | Changing:<br>State Not Known       |

|          | N/A                               | Center Line is<br>High Impedance   |

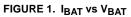

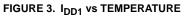

FIGURE 2.  $I_{BAT}$  vs TEMPERATURE AT  $V_{BAT}$  = 3V

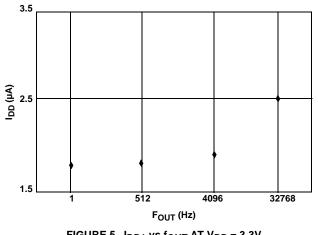

FIGURE 5.  $I_{DD1}$  vs  $f_{OUT}$  AT  $V_{DD}$  = 3.3V

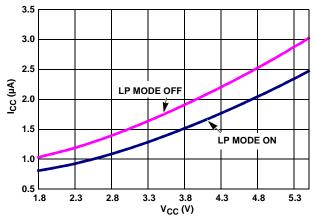

FIGURE 4. I<sub>DD1</sub> vs V<sub>CC</sub> WITH LPMODE ON AND OFF

FIGURE 7. STANDARD OUTPUT LOAD FOR TESTING THE DEVICE WITH  $V_{\rm DD}$  = 5.0V

### **General Description**

The ISL12082 device is a low power real time clock with timing and crystal compensation, clock/calendar, power fail indicator, periodic or polled alarm, timer/watchdog, and intelligent battery backup switching.

The oscillator uses an external, low-cost 32.768kHz crystal. The real time clock tracks time with separate registers for hours, minutes, seconds, and sub-seconds. The device has calendar registers for date, month, year and day of the week. The calendar is accurate through 2099, with automatic leap year correction.

The ISL12082's powerful alarm can be set to any clock/calendar value for a match. For example, every minute, every Tuesday or at 5:23 AM on March 21. The alarm status is available by checking the Status Register, or the device can be configured to provide a hardware interrupt via the IRQ1/f<sub>OUT</sub> or IRQ2 pin. There is a repeat mode for the alarm allowing a periodic interrupt every minute, every hour, every day, etc.

The ISL12082 has a powerful timer function. The timer status is available by checking the Status Register, or the device can be configured to provide a hardware interrupt via the IRQ2 pin.

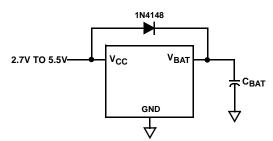

The device also offers a backup power input pin. This  $V_{BAT}$  pin allows the device to be backed up by battery or Supercapacitor with automatic switchover from  $V_{DD}$  to  $V_{BAT}$ . The entire ISL12082 device is fully operational from 2.7V to 5.5V and the clock/calendar portion of the device remains fully operational down to 1.8V (Standby Mode).

## **Pin Description**

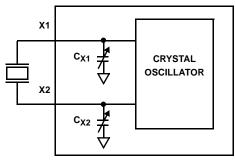

### X1, X2

The X1 and X2 pins are the input and output, respectively, of an inverting amplifier. An external 32.768kHz quartz crystal is used with the ISL12082 to supply a timebase for the real time clock. Internal compensation circuitry provides high accuracy over the operating temperature range from -40°C to +85°C. This oscillator compensation network can be used to calibrate the crystal timing accuracy over-temperature either during manufacturing or with an external temperature sensor and microcontroller for active compensation. The device can also be driven directly from a 32.768kHz source at pin X1.

8

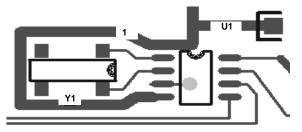

FIGURE 8. RECOMMENDED CRYSTAL CONNECTION

## V<sub>BAT</sub>

This input provides a backup supply voltage to the device.  $V_{BAT}$  supplies power to the device in the event that the  $V_{DD}$  supply fails. This pin can be connected to a battery, a Supercapacitor or tied to ground if not used.

## IRQ1/f<sub>OUT</sub> (Interrupt Output 1/Frequency Output)

The  $\overline{IRQ1}/f_{OUT}$  is an open drain output.

This dual function pin can be used as an interrupt or frequency output pin. The  $\overline{IRQ1}/f_{OUT}$  mode is selected via the IRQ1E bit of the control register (address 08h).

- Interrupt Mode. The pin provides an interrupt signal output. This signal notifies a host processor that an alarm has occurred and requests action.

- Frequency Output Mode. The pin outputs a clock signal which is related to the crystal frequency. The frequency output is user selectable and enabled via the I<sup>2</sup>C bus.

## IRQ2 (Interrupt Output 2)

The IRQ2 is an open drain output.

The  $\overline{IRQ2}$  pin can be used as an alarm interrupt or timer interrupt output pin. The  $\overline{IRQ2}$  mode is selected via the IRQ2E control bits of the control register (address 08h). The pin provides an interrupt signal output. This signal notifies a host processor that an alarm or timer has occurred and requests action.

### Serial Clock (SCL)

The SCL input is used to clock all serial data into and out of the device. The input buffer on this pin is always active (not gated). It is disabled when the backup power supply on the  $V_{BAT}$  pin is activated to minimize power consumption.

#### Serial Data (SDA)

SDA is a bi-directional pin used to transfer data into and out of the device. It has an open drain output and may be ORed with other open drain or open collector outputs. The input buffer is always active (not gated) in normal mode.

An open drain output requires the use of a pull-up resistor. The output circuitry controls the fall time of the output signal with the use of a slope controlled pull-down. The circuit is designed for 400kHz  $I^2C$  interface speeds. It is disabled when the backup power supply on the V<sub>BAT</sub> pin is activated.

### V<sub>DD</sub>, GND

Chip power supply and ground pins. The device will operate with a power supply from 2.7V to 5.5VDC. A  $0.1 \mu F$

decoupling capacitor is recommended on the  $\ensuremath{\mathsf{V}_{\text{DD}}}$  pin to ground.

## **Functional Description**

#### **Power Control Operation**

The power control circuit accepts a V<sub>DD</sub> and a V<sub>BAT</sub> input. Many types of batteries can be used with Intersil RTC products. For example, 3.0V or 3.6V Lithium batteries are appropriate, and battery sizes are available that can power the ISL12082 for up to 10 years. Another option is to use a Supercapacitor for applications where V<sub>DD</sub> is interrupted for up to a month. See the "Application Section" on page 22 for more information.

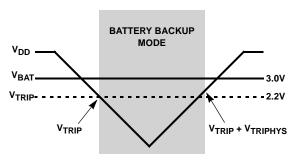

## Normal Mode ( $V_{DD}$ ) to Battery Backup Mode ( $V_{BAT}$ )

To transition from the  $V_{DD}$  to  $V_{BAT}$  mode,  $\underline{both}$  of the following conditions must be met:

#### Condition 1:

$V_{DD} < V_{BAT} - V_{BATHYS}$ where  $V_{BATHYS} \approx 50 \text{mV}$

#### Condition 2:

$V_{DD} < V_{TRIP}$ where  $V_{TRIP} \approx 2.2V$

## Battery Backup Mode ( $V_{BAT}$ ) to Normal Mode ( $V_{DD}$ )

The ISL12082 device will switch from the  $V_{BAT}$  to  $V_{DD}$  mode when  $\underline{one}$  of the following conditions occurs:

#### Condition 1:

$$\label{eq:VDD} \begin{split} V_{DD} &> V_{BAT} + V_{BATHYS} \\ \text{where } V_{BATHYS} \approx 50 \text{mV} \end{split}$$

#### Condition 2:

$V_{DD} > V_{TRIP} + V_{TRIPHYS}$ where  $V_{TRIPHYS} \approx 30 mV$

These power control situations are illustrated in Figures 9 and 10.

#### FIGURE 10. BATTERY SWITCHOVER WHEN VBAT > VTRIP

The I<sup>2</sup>C bus is deactivated in battery backup mode to provide lower power. Aside from this, all RTC functions are operational during battery backup mode. Except for SCL and SDA, all the inputs and outputs of the ISL12082 are active during battery backup mode unless disabled via the control register.

#### **Power Failure Detection**

The ISL12082 provides a Real Time Clock Failure Bit (RTCF, address 0Bh) to detect total power failure. It allows users to determine if the device has powered up after having lost all power to the device (both  $V_{DD}$  and  $V_{BAT}$ ).

#### Low Power Mode

The normal power switching of the ISL12082 is designed to switch into battery backup mode only if the V<sub>DD</sub> power is lost. This will ensure that the device can accept a wide range of backup voltages from many types of sources while reliably switching into backup mode. Another mode, called Low Power Mode, is available to allow direct switching from V<sub>DD</sub> to V<sub>BAT</sub> without requiring V<sub>DD</sub> to drop below V<sub>TRIP</sub>. Since the additional monitoring of V<sub>DD</sub> vs V<sub>TRIP</sub> is no longer needed, that circuitry is shut down and less power is used while operating from V<sub>DD</sub>. Power savings are typically 600nA at V<sub>DD</sub> = 5V. Low Power Mode is activated via the LPMODE bit in the control and status registers.

Low Power Mode is useful in systems where  $V_{DD}$  is normally higher than  $V_{BAT}$  at all times. The device will switch from  $V_{DD}$  to  $V_{BAT}$  when  $V_{DD}$  drops below  $V_{BAT}$ , with about 50mV of hysteresis to prevent any switchback of  $V_{DD}$  after switchover. In a system with a  $V_{DD}$  = 5V and backup lithium battery of  $V_{BAT}$  = 3V, Low Power Mode can be used. However, it is not recommended to use Low Power Mode in a system with  $V_{DD}$  = 3.3V ±10%,  $V_{BAT} \ge$  3.0V, and when there is a finite I-R voltage drop in the  $V_{DD}$  line.

#### InterSeal<sup>™</sup> and ReSeal<sup>™</sup> Battery Saver

The ISL12082 has the InterSeal<sup>TM</sup> Battery Saver, which prevents initial battery current drain before it is first used. For example, battery-backed RTCs are commonly packaged on a board with a battery connected. In order to preserve battery life, the ISL12082 will not draw any power from the battery source until after the device is first powered up from the V<sub>DD</sub> source. Thereafter, the device will switchover to battery backup mode whenever V<sub>DD</sub> power is lost. The ISL12082 has the ReSeal<sup>™</sup> function, which allows the device to enter into the InterSeal<sup>™</sup> Battery Saver mode after manufacture testing for board functionality. To use the ReSeal<sup>™</sup> function, simply set RESEAL bit to "1" (address 07h) after the testing is completed. It will enable the InterSeal<sup>™</sup> Battery Saver mode and prevents battery current drain before it is first used.

## Real Time Clock Operation

The Real Time Clock (RTC) uses an external 32.768kHz quartz crystal to maintain an accurate internal representation of sub-second, second, minute, hour, day of week, date, month, and year. The RTC also has leap-year correction. The RTC also corrects for months having fewer than 31 days and has a bit that controls 24 hour or AM/PM format. When the ISL12082 powers up after the loss of both  $V_{DD}$  and  $V_{BAT}$ , the clock will not begin incrementing until at least one byte is written to the clock register.

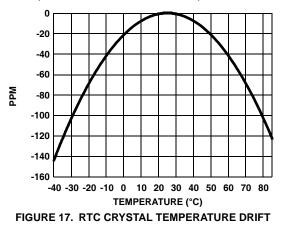

#### Accuracy of the Real Time Clock

The accuracy of the Real Time Clock depends on the frequency of the quartz crystal that is used as the time base for the RTC. Since the resonant frequency of a crystal is temperature dependent, the RTC performance will also be dependent upon temperature. The frequency deviation of the crystal is a function of the turnover-temperature of the crystal from the crystal's nominal frequency. For example, a ~20ppm frequency deviation translates into an accuracy of ~1 minute per month. These parameters are available from the crystal manufacturer. The ISL12082 provides on-chip crystal compensation networks to adjust load capacitance to tune oscillator frequency from -94ppm to +140ppm. For more detailed information, see "Application Section" on page 22.

#### Single Event and Interrupt

The alarm mode is enabled via the ALME bit (address 08h). Choosing single event or interrupt alarm mode is selected via the IM bit (address 08h). Note that when the frequency output function is enabled, the alarm function is disabled.

The standard alarm allows for alarms of time, date, day of the week, month, and year. When a time alarm occurs in single event mode, an IRQ1/f<sub>OUT</sub> and/or IRQ2 pin will be pulled low and the alarm status bit (ALM) will be set to "1".

The pulsed interrupt mode allows for repetitive or recurring alarm functionality. Hence, once the alarm is set, the device will continue to alarm for each occurring match of the alarm and present time. Thus, it will alarm as often as every minute (if only the nth second is set) or as infrequently as once a year (if at least the nth month is set). During pulsed interrupt mode, the  $\overline{IRQ1}/f_{OUT}$  and/or  $\overline{IRQ2}$  pin will be pulled low for 210ms and the alarm status bit (ALM) will be set to "1".

Note: The ALM bit can be reset by the user or cleared automatically using the auto reset mode (see ARST bit, address 07h).

The alarm function can be enabled/disabled during battery backup mode using the FOBATB bit (address 08h). For more information on the alarm, see "Alarm Registers" on page 14.

#### Frequency Output Mode

The ISL12082 has the option to provide a frequency output signal using the  $\overline{IRQ}/f_{OUT}$  pin. The frequency output mode is set by using the FO bits to select 4 possible output frequency values from 1kHz to 32.768kHz. The frequency output can be enabled/disabled during battery backup mode using the FOBATB bit (address 08h).

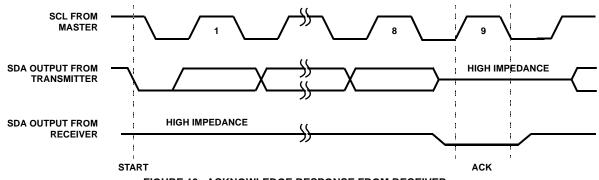

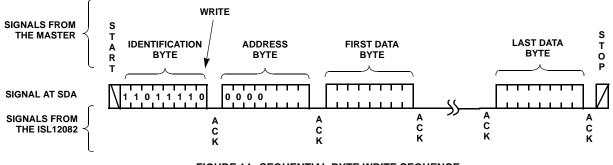

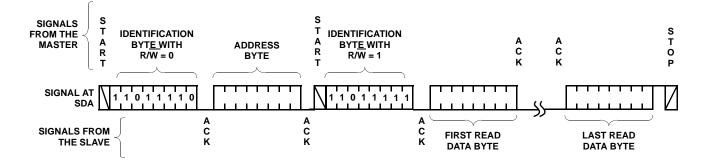

#### I<sup>2</sup>C Serial Interface

The ISL12082 has an  $I^2C$  serial bus interface that provides access to the control and status registers and the user SRAM. The  $I^2C$  serial interface is compatible with other industry  $I^2C$  serial bus protocols using a bi-directional data signal (SDA) and a clock signal (SCL).

#### **Oscillator Compensation**

The ISL12082 provides the option of timing correction due to temperature variation of the crystal oscillator for either manufacturing calibration or active calibration. The total possible compensation is typically -94ppm to +140ppm. Two compensation mechanisms that are available are as follows:

- An analog trimming (ATR) register that can be used to adjust individual on-chip digital capacitors for oscillator capacitance trimming. The individual digital capacitor is selectable from a range of 9pF to 40.5pF (based upon 32.758kHz). This translates to a calculated compensation of approximately -34ppm to +80ppm. See "ATR description" on page 22.

- 2. A digital trimming register (DTR) that can be used to adjust the timing counter by -63ppm to +126ppm. See "DTR description" on page 22.

Also provided is the ability to adjust the crystal capacitance when the ISL12082 switches from  $\mathsf{V}_{\mathsf{DD}}$  to battery backup mode.

## **Register Descriptions**

The battery-backed registers are accessible following a slave byte of "1101111x" and reads or writes to addresses [00h:1Fh]. The defined addresses and default values are described in Table 1. Address 16h to 1Eh are not used. Reads or writes to addresses 16h to 1Eh will not affect operation of the device but should be avoided.

#### **Register Access**

The contents of the registers can be modified by performing a byte or a page write operation directly to any register address.

The registers are divided into 4 sections. These are:

- 1. Real Time Clock (8 bytes): Address 00h to 06h, and 1Fh, with address 1Fh as read-only byte.

- 2. Control and Status (5 bytes): Address 07h to 0Bh.

- 3. Alarm (6 bytes): Address 0Ch to 11h.

- 4. TIMER (4 bytes): Address 12h to 14h, with address 14h as write-only byte and read back '0'..

There are no addresses above 1Fh.

Address 15h to 1Eh are not used. Reads or writes to addresses 15h to 1Eh will not affect operation of the device but should be avoided.

Write capability is allowable into the RTC registers (00h to 06h, and 1Fh) only when the WRTC bit (bit 4 of address 07h) is set to "1". A multi-byte read or write operation is limited to one section per operation. Access to another section requires a new operation. A read or write can begin at any address within the section.

A register can be read by performing a random read at any address at any time. This returns the contents of that register location. Additional registers are read by performing a sequential read. For the RTC and alarm registers, the read instruction latches all clock registers into a buffer, so an update of the clock does not change the time being read. A sequential read will not result in the output of data from the memory array. At the end of a read, the master supplies a stop condition to end the operation and free the bus. After a read, the address remains at the previous address +1 so the user can execute a current address read and continue reading the next register.

|       |         | REG   |        | BIT    |        |        |        |        |        |        |          | REG     |  |

|-------|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|----------|---------|--|

| ADDR. | SECTION | NAME  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | RANGE    | DEFAULT |  |

| 1Fh   | RTC     | SS    | SS23   | SS22   | SS21   | SS20   | SS13   | SS12   | SS11   | SS10   | 0 to 99  | 00h     |  |

| 00h   |         | SC    | 0      | SC22   | SC21   | SC20   | SC13   | SC12   | SC11   | SC10   | 0 to 59  | 00h     |  |

| 01h   |         | MN    | OF     | MN22   | MN21   | MN20   | MN13   | MN12   | MN11   | MN10   | 0 to 59  | 80h     |  |

| 02h   |         | HR    | MIL    | 0      | HR21   | HR20   | HR13   | HR12   | HR11   | HR10   | 0 to 23  | 00h     |  |

| 03h   |         | DT    | 0      | 0      | DT21   | DT20   | DT13   | DT12   | DT11   | DT10   | 1 to 31  | 00h     |  |

| 04h   |         | MO    | 0      | 0      | 0      | MO20   | MO13   | MO12   | MO11   | MO10   | 1 to 12  | 00h     |  |

| 05h   |         | YR    | YR23   | YR22   | YR21   | YR20   | YR13   | YR12   | YR11   | YR10   | 0 to 99  | 00h     |  |

| 06h   |         | DW    | 0      | 0      | 0      | 0      | 0      | DW12   | DW11   | DW10   | 0 to 6   | 00h     |  |

| 07h   | Status  | SR    | ARST   | XSTOP  | RESEAL | WRTC   | TMR    | ALM    | BAT    | RTCF   | N/A      | 03h     |  |

| 08h   | Control | INT   | IM     | ALME   | LPMODE | FOBATB | IRQ2E  | IRQ1E  | FO1    | FO0    | N/A      | 00h     |  |

| 09h   |         | TMRC  | TIM    | TMRE   | TMOD1  | TMOD0  | 0      | 0      | TCLK1  | TCLK0  | N/A      | 00h     |  |

| 0Ah   |         | ATR   | BMATR1 | BMATR0 | ATR5   | ATR4   | ATR3   | ATR2   | ATR1   | ATR0   | N/A      | 00h     |  |

| 0Bh   |         | DTR   | 0      | 0      | DTR5   | DTR4   | DTR3   | DTR2   | DTR1   | DTR0   | N/A      | 80h     |  |

| 0Ch   |         | SCA   | ESCA   | ASC22  | ASC21  | ASC20  | ASC13  | ASC12  | ASC11  | ASC10  | 00 to 59 | 00h     |  |

| 0Dh   |         | MNA   | EMNA   | AMN22  | AMN21  | AMN20  | AMN13  | AMN12  | AMN11  | AMN10  | 00 to 59 | 00h     |  |

| 0Eh   | Alarm0  | HRA   | EHRA   | 0      | AHR21  | AHR20  | AHR13  | AHR12  | AHR11  | AHR10  | 0 to 23  | 00h     |  |

| 0Fh   | Alainio | DTA   | EDTA   | 0      | ADT21  | ADT20  | ADT13  | ADT12  | ADT11  | ADT10  | 1 to 31  | 00h     |  |

| 10h   |         | MOA   | EMOA   | 0      | 0      | AMO20  | AMO13  | AMO12  | AMO11  | AMO10  | 1 to 12  | 00h     |  |

| 11h   |         | DWA   | EDWA   | 0      | 0      | 0      | 0      | ADW12  | ADW11  | ADW10  | 0 to 6   | 00h     |  |

| 12h   |         | TDAT  | TDAT7  | TDAT6  | TDAT5  | TDAT4  | TDAT3  | TDAT2  | TDAT1  | TDAT0  | 0 to 255 | 00h     |  |

| 13h   | TIMER   | TCNT  | TCNT7  | TCNT6  | TCNT5  | TCNT4  | TCNT3  | TCNT2  | TCNT1  | TCNT0  | 0 to 255 | 00h     |  |

| 14h   |         | TSDAT | Х      | TSDAT6 | TSDAT5 | TSDAT4 | TSDAT3 | TSDAT2 | TSDAT1 | TSDAT0 | 0 to 99  | 00h     |  |

#### TABLE 1. REGISTER MEMORY MAP

## Real Time Clock Registers

#### Addresses [00h to 06h, and 1Fh]

#### RTC REGISTERS (SC, MN, HR, DW, DT, MO, YR, SS)

These registers depict BCD representations of the time. As such, SC (Seconds, address 00h) and MN (Minutes, address 01h) range from 0 to 59, HR (Hour, address 02h) can either be a 12-hour or 24-hour mode, DT (Date, address 03h) is 1 to 31, MO (Month, address 04h) is 1 to 12, YR (Year, address 05h) is 0 to 99, DW (Day of the Week, address 03h) is 0 to 6, and SS (Sub-Seconds/Hundredths of a Second, address 1Fh) is 0 to 99. The SS register is read only. A Page read operation to read all the RTC regsiters is possible by setting up the address to 1Fh then do a page read of 8 bytes. The first data read will be SS, then follows by SC, MN, HR, DT, MO, YR, and DW at the end. This is done by using address wrap around feature of the ISL12082. The address wraps around from 1Fh to 00h in page read instruction.

The DW register provides a Day of the Week status and uses three bits DW2 to DW0 to represent the seven days of the week. The counter advances in the cycle 0-1-2-3-4-5-6-0-1-2-... The assignment of a numerical value to a specific day of the week is arbitrary and may be decided by the system software designer. The default value is defined as "0".

Bit D7 of MN register contains the Oscillator Fail Indicator bit (OF). This bit is set to a "1" when there is no oscillation on X1 pin. The OF bit can only be reset by having an oscillation on X1 and a write operation to reset it.

#### 24 HOUR TIME

If the MIL bit of the HR register is "1", the RTC uses a 24hour format. If the MIL bit is "0", the RTC uses a 12-hour format and HR21 bit functions as an AM/PM indicator with a "1" representing PM. The clock defaults to 12-hour formattime with HR21 = "0".

#### LEAP YEARS

Leap years add the day February 29 and are defined as those years that are divisible by 4. Years divisible by 100 are not leap years, unless they are also divisible by 400. This means that the year 2000 is a leap year, the year 2100 is not. The ISL12082 does not correct for the leap year in the year 2100.

## **Control and Status Registers**

#### Addresses [07h to 0Bh]

The Control and Status Registers consist of the Status Register, Interrupt and alarm register, Analog Trimming and Digital Trimming Registers.

#### Status Register (SR) [Address 07h]

The Status Register is located in the memory map at address 0Bh. This is a volatile register that provides either control or status of RTC failure, battery mode, alarm trigger, write protection of clock counter, crystal oscillator enable and auto reset of status bits.

TABLE 2. STATUS REGISTER (SR)

| ADDR    | 7    | 6     | 5      | 4    | 3   | 2   | 1   | 0    |

|---------|------|-------|--------|------|-----|-----|-----|------|

| 07h     | ARST | XSTOP | RESEAL | WRTC | TMR | ALM | BAT | RTCF |

| Default | 0    | 0     | 1      | 0    | 0   | 0   | 1   | 1    |

#### REAL TIME CLOCK FAIL BIT (RTCF)

This bit is set to a "1" after a total power failure. This is a read only bit that is set by hardware (ISL12082 internally) when the device powers up after having lost all power (both  $V_{DD}$  and  $V_{BAT}$  go to 0V). The bit is set regardless of whether  $V_{DD}$  or  $V_{BAT}$  is applied first. The loss of only one of the supplies does not set the RTCF bit to "1". On power-up after a total power failure, all registers are set to their default states and the clock will not increment until at least one byte is written to the clock register. The first valid write to the RTCF bit to "0" (writing one byte is sufficient).

#### BATTERY BIT (BAT)

This bit is set to a "1" when the device enters battery backup mode. This bit can be reset either manually by the user or automatically reset by enabling the auto-reset bit (see ARST bit). A write to this bit in the SR can only set it to "0", not "1".

#### ALARM BIT (ALM)

This bit announces that the alarm matches the real time clock. If there is a match, the respective bit is set to "1". This bit can be manually reset to "0" by the user or automatically reset by enabling the auto-reset bit (see ARST bit). A write to this bit in the SR can only set it to "0", not "1".

Note: An alarm bit that is set by an alarm occurring during an SR read operation will remain set after the read operation is complete.

#### TIMER BIT (TMR)

This bit announces that the timer has expired. If the timer has expired, the respective bit is set to "1". This bit can be manually reset to "0" by the user or automatically reset by enabling the auto-reset bit (see ARST bit). A write to this bit in the SR can only set it to "0", not "1".

#### WRITE RTC ENABLE BIT (WRTC)

The WRTC bit enables or disables write capability into the RTC Timing Registers. The factory default setting of this bit is "0". Upon initialization or power-up, the WRTC must be set to "1" to enable the RTC. Upon the completion of a valid write (STOP), the RTC starts counting. The RTC internal 1Hz signal is synchronized to the STOP condition during a valid write cycle.

#### ReSeal™ (RESEAL)

The ReSeal<sup>™</sup> enables the device enter into the InterSeal<sup>™</sup> Battery Saver mode after board functional testing. The factory default setting of this bit is "0" to enable the backup battery operation. To use the ReSeal<sup>TM</sup> function, simply set RESEAL bit to "1" after the testing is completed. It will enable the InterSeal<sup>TM</sup> Battery Saver mode and prevents battery current drain before it is first used. Upon the next V<sub>DD</sub> powerup, the bit will reset to "0" and the backup battery will be utilized.

#### **CRYSTAL OSCILLATOR ENABLE BIT (XSTOP)**

This bit enables/disables the crystal oscillator. When the XSTOP is set to "1", the oscillator is disabled. The XSTOP bit is set to "0" on power-up for normal operation.

#### AUTO RESET ENABLE BIT (ARST)

This bit enables/disables the automatic reset of the BAT, ALM and TMR status bits only. When ARST bit is set to "1", these status bits are reset to "0" after a valid read of the respective status register (with a valid STOP condition). When the ARST is cleared to "0", the user must manually reset the BAT, ALM and TMR bits.

#### Interrupt Control Register (INT) [Address 08h]

#### TABLE 3. INTERRUPT CONTROL REGISTER (INT)

| ADDR    | 7  | 6    | 5      | 4      | 3     | 2     | 1   | 0   |

|---------|----|------|--------|--------|-------|-------|-----|-----|

| 08h     | IM | ALME | LPMODE | FOBATB | IRQ2E | IRQ1E | FO1 | FO0 |

| Default | 0  | 0    | 0      | 0      | 0     | 0     | 0   | 0   |

#### FREQUENCY OUT CONTROL BITS (FO <1:0>)

These bits select the output frequency at the  $\overline{IRQ}/f_{OUT}$  pin. IRQ1E must be set to "0" for frequency output at the IRQ/f<sub>OUT</sub> pin. See Table 4 for frequency selection.

| FREQUENCY,<br><sup>f</sup> out | UNITS | FO1 | FO0 | COMMENT                           |

|--------------------------------|-------|-----|-----|-----------------------------------|

| 32768                          | Hz    | 0   | 0   | Free running<br>crystal clock     |

| 4096                           | Hz    | 0   | 1   | Free running<br>crystal clock     |

| 512                            | Hz    | 1   | 0   | Free running<br>crystal clock     |

| 1                              | Hz    | 1   | 1   | Sync. with<br>second, 30µs jitter |

#### TABLE 4. FREQUENCY SELECTION OF fOUT PIN

Note: The falling edge of 1Hz frequency output is synchronized with the seconds.

#### **IRQ FUNCTION SELECTION BITS (IRQ1E, IRQ2E)**

These bits select the function of  $\overline{IRQ1}/f_{OUT}$  and  $\overline{IRQ2}$  pin. See Table 5 for function selection of  $\overline{IRQ1}/f_{OUT}$  pin and Table 6 for function selection of  $\overline{IRQ2}$  pin.

#### TABLE 5. FUNCTION SELECTION OF IRQ1/fOUT

PIN

| IRQ1/f <sub>OUT</sub> FUNCTION | IRQ2E | IRQ1E |

|--------------------------------|-------|-------|

| fout                           | Х     | 0     |

#### TABLE 5. FUNCTION SELECTION OF IRQ1/f<sub>OUT</sub> PIN (Continued)

| IRQ1/fOUT FUNCTION | IRQ2E | IRQ1E |

|--------------------|-------|-------|

| ALARM IRQ          | Х     | 1     |

#### TABLE 6. FUNCTION SELECTION OF IRQ2 PIN

| IRQ2 FUNCTION | IRQ2E | IRQ1E |

|---------------|-------|-------|

| ALARM IRQ     | 0     | Х     |

| TIMER IRQ     | 1     | Х     |

#### FREQUENCY OUTPUT AND INTERRUPT BIT (FOBATB)

This bit enables/disables the  $\overline{IRQ1}/f_{OUT}$  pin during battery backup mode (i.e.  $V_{BAT}$  power source active). When the FOBATB is set to "1", the  $\overline{IRQ1}/f_{OUT}$  pin is disabled during battery backup mode. This means that both the frequency output and alarm output functions are disabled. When the FOBATB is cleared to "0", the  $\overline{IRQ1}/f_{OUT}$  pin is enabled during battery backup mode.

#### LOW POWER MODE BIT (LPMODE)

This bit enables/disables low power mode. With LPMODE = "0", the device will be in normal mode and the V<sub>BAT</sub> supply will be used when V<sub>DD</sub> < V<sub>BAT</sub> - V<sub>BATHYS</sub> and V<sub>DD</sub> < V<sub>TRIP</sub>. With LPMODE = "1", the device will be in low power mode and the V<sub>BAT</sub> supply will be used when V<sub>DD</sub> < V<sub>BAT</sub> - V<sub>BATHYS</sub>. There is a supply current saving of about 600nA when using LPMODE = "1" with V<sub>DD</sub> = 5V (See "Typical Performance Curves" on page 7: I<sub>DD</sub> vs V<sub>CC</sub> with LPMODE ON and OFF). see also "Power Control Operation" under "Functional Description" on page 9.

#### ALARM ENABLE BIT (ALME)

This bit enables/disables the alarm function. When the ALME bit is set to "1", the alarm function is enabled. When the ALME is cleared to "0", the alarm function is disabled. The alarm function can operate in either a single event alarm or a periodic interrupt alarm (see IM bit).

Note: When the frequency output mode is enabled, the alarm function is disabled.

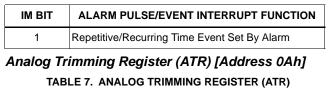

#### ALARM PULSE/EVENT INTERRUPT BIT (IM)

This bit enables/disables the interrupt mode of the alarm function. When the IM bit is set to "1", the alarm will operate in the interrupt mode, where an active low pulse width of 210ms will appear at the  $IRQ1/f_{OUT}$  and/or IRQ2 pin when the RTC is triggered by the alarm as defined by the alarm registers (0Ch to 11h). When the IM bit is cleared to "0", the alarm will operate in standard mode, where the  $IRQ1/F_{OUT}$  and/or IRQ2 pin will be tied low until the ALM status bit is cleared to "0". The IM bit is set to "0" on power-up.

| IM BIT | ALARM PULSE/EVENT INTERRUPT FUNCTION |

|--------|--------------------------------------|

| 0      | Single Time Event Set By Alarm       |

| ADDR    | 7      | 6      | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|--------|--------|------|------|------|------|------|------|

| 0Ah     | BMATR1 | BMATR0 | ATR5 | ATR4 | ATR3 | ATR2 | ATR1 | ATR0 |

| Default | 0      | 0      | 0    | 0    | 0    | 0    | 0    | 0    |

#### ANALOG TRIMMING REGISTER (ATR<5:0>)

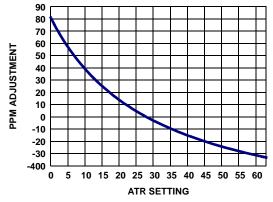

FIGURE 11. DIAGRAM OF ATR

Six analog trimming bits, **ATR0** to **ATR5**, are provided in order to adjust the on-chip load capacitance value for frequency compensation of the RTC. Each bit has a different weight for capacitance adjustment. For example, using a Citizen CFS-206 crystal with different ATR bit combinations provides an estimated ppm adjustment range from -34ppm to +80ppm to the nominal frequency compensation. The combination of analog and digital trimming can give up to -97ppm to +206ppm of total adjustment.

The effective on-chip series load capacitance,  $C_{LOAD}$ , ranges from 4.5pF to 20.25pF with a mid-scale value of 12.5pF (default).  $C_{LOAD}$  is changed via two digitally controlled capacitors,  $C_{X1}$  and  $C_{X2}$ , connected from the X1 and X2 pins to ground (see Figure 11). The value of  $C_{X1}$  and  $C_{X2}$  are given in Equation 1:

$C_{\chi} = (16 \cdot \overline{b5} + 8 \cdot b4 + 4 \cdot b3 + 2 \cdot b2 + 1 \cdot b1 + 0.5 \cdot b0 + 9)pF \quad (EQ. 1)$

The effective series load capacitance is the combination of  $C_{X1}$  and  $C_{X2}$  in Equation 2:

$$C_{LOAD} = \frac{1}{\left(\frac{1}{C_{X1}} + \frac{1}{C_{X2}}\right)}$$

(EQ. 2)

$$C_{LOAD} = \left(\frac{16 \cdot \overline{b5} + 8 \cdot b4 + 4 \cdot b3 + 2 \cdot b2 + 1 \cdot b1 + 0.5 \cdot b0 + 9}{2}\right) pF$$

For example,  $C_{LOAD}(ATR = 00000) = 12.5pF$ ,  $C_{LOAD}(ATR = 100000) = 4.5pF$  and  $C_{LOAD}(ATR = 011111) = 20.25pF$ . The entire range for the series combination of load capacitance goes from 4.5pF to 20.25pF in 0.25pF steps. Note that these are typical values.

#### BATTERY MODE ATR SELECTION (BMATR <1:0>)

Since the accuracy of the crystal oscillator is dependent on the V\_DD/V\_BAT operation, the ISL12082 provides the capability to adjust the capacitance between V\_DD and V\_BAT when the device switches between power sources.

| BMATR1 | BMATR0 | DELTA<br>CAPACITANCE<br>(C <sub>BAT</sub> TO C <sub>VDD</sub> ) |

|--------|--------|-----------------------------------------------------------------|

| 0      | 0      | 0pF                                                             |

| 0      | 1      | -0.5pF (≈ +2ppm)                                                |

| 1      | 0      | +0.5pF (≈ -2ppm)                                                |

| 1      | 1      | +1pF (≈ -4ppm)                                                  |

## Digital Trimming Register (DTR) [Address 07h]

TABLE 8. DIGITAL TRIMMING REGISTER (DTR)

| ADDR    | 7 | 6 | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|---|---|------|------|------|------|------|------|

| 07h     | 0 | 0 | DTR5 | DTR4 | DTR3 | DTR2 | DTR1 | DTR0 |

| Default | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0    |

#### DIGITAL TRIMMING REGISTER (DTR<5:0>)

Six digital trimming bits, **DTR0** to **DTR5**, are provided to adjust the average number of counts per second and average the ppm error to achieve better accuracy.

- DTR5 is a sign bit. DTR5 = "0" means frequency compensation is < 0. DTR5 = "1" means frequency compensation is > 0.

- DTR<4:0> are scale bits. With DTR5 = "0", DTR<4:0> gives 2.0345ppm adjustment per step. With DTR5 = "1", DTR<4:0> gives 4.0690ppm adjustment per step.

A range from -63.0696ppm to +126.139ppm can be represented by using these 6 bits.

For example, with DTR = 11111, the digital adjustment is  $(1111b[15d]^{4}.0690) = +126.139ppm$ . With DTR = 01111, the digital adjustment is  $(-(1111b[15d]^{2}.0345)) = -63.0696ppm$ .

## Alarm Registers

#### Addresses [Address 0Ch to 11h]

The alarm register bytes are set up identical to the RTC register bytes, except that the MSB of each byte functions as an enable bit (enable = "1"). These enable bits specify which alarm registers (seconds, minutes, etc) are used to make the comparison. Note that there is no alarm byte for year and sub-second, and the register order for alarm register is not a 100% matching to the RTC register so please take caution on programming the alarm function.

The alarm function works as a comparison between the alarm registers and the RTC registers. As the RTC advances, the alarm will be triggered once a match occurs between the alarm registers and the RTC registers. Any one alarm register, multiple registers, or all registers can be enabled for a match.

There are two alarm operation modes: Single Event and Periodic Interrupt Mode:

- Single Event Mode is enabled by setting the ALME bit to "1", the IM bit to "0", and IRQ1E bit to "1" and/or IRQ2E bit to "0". This mode permits a <u>one-time</u> match between the alarm registers and the RTC registers. Once this match occurs, the ALM status bit is set to "1" and the IRQ1/f<sub>OUT</sub> and/or IRQ2 output will be pulled low and will remain low until the ALM status bit is reset to "0". This can be done manually or by using the auto-reset feature.

- Periodic Interrupt Mode is enabled by setting the ALME bit to "1", the IM bit to <u>"1"</u>, and IRQ1E bit to <u>"1"</u> and/or IRQ2E bit to "0". The IRQ1/f<sub>OUT</sub> and/or IRQ2 output will now be pulsed <u>each time</u> an alarm occurs. This means that once the interrupt mode alarm is set, it will continue to alarm for each occurring match of the alarm and present time. This mode is convenient for hourly or daily hardware interrupts in microcontroller applications such as security cameras or utility meter reading.

To clear an alarm, the ALM status bit must be set to "0" with a write. Note that if the ARST bit is set to "1" (address 07h, Bit 7), the ALM bit will automatically be cleared when the status register is read.

Following are examples of both Single Event and periodic Interrupt Mode alarms.

#### Example 1 – Alarm set with single interrupt (IM = "0")

A single alarm will occur on January 1 at 11:30am.

| Δ  | Set Alarm | registers | as follows: |  |

|----|-----------|-----------|-------------|--|

| л. |           | registers | as 10110WS. |  |

| ALARM    |   |   |   |   | В |   |   |   |     |                             |

|----------|---|---|---|---|---|---|---|---|-----|-----------------------------|

| REGISTER | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | HEX | DESCRIPTION                 |

| SCA      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Seconds disabled            |

| MNA      | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | B0h | Minutes set to 30, enabled  |

| HRA      | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 91h | Hours set to 11,<br>enabled |

| DTA      | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 81h | Date set to 1,<br>enabled   |

| MOA      | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 81h | Month set to 1, enabled     |

| DWA      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Day of week<br>disabled     |

B. Set the ALME bit as follows:

| CONTROL  |   |   |   |   | В | Т |   |   |     |              |

|----------|---|---|---|---|---|---|---|---|-----|--------------|

| REGISTER | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | HEX | DESCRIPTION  |

| INT      | 0 | 1 | х | х | 0 | 0 | 0 | 0 | x0h | Enable Alarm |

NOTE: x indicate other control bits

After these registers are set, an alarm will be generated when the RTC advances to exactly 11:30am on January 1 (after seconds changes from 59 to 00) by setting the ALM bit in the status register to "1" and also bringing the IRQ1/f<sub>OUT</sub> and IRQ2 output low if IRQ1E bit is set to "1" and IRQ2E bit is set to "0".

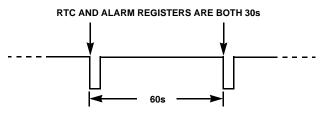

## Example 2 – Pulsed interrupt once per minute (IM = "1")

Interrupts at one minute intervals when the seconds register is at 30s.

| Δ  | Set | alarm  | registers | as | follows   |

|----|-----|--------|-----------|----|-----------|

| л. | OCI | alainn | registers | as | 10110103. |

| ALARM    |   | BIT |   |   |   |   |   |   |     |                            |

|----------|---|-----|---|---|---|---|---|---|-----|----------------------------|

| REGISTER | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0 | HEX | DESCRIPTION                |

| SCA      | 1 | 0   | 1 | 1 | 0 | 0 | 0 | 0 | B0h | Seconds set to 30, enabled |

| MNA      | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Minutes disabled           |

| HRA      | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Hours disabled             |

| DTA      | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Date disabled              |

| MOA      | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Month disabled             |

| DWA      | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 00h | Day of week disabled       |

B. Set the Interrupt register as follows:

| CONTROL  |   |   |   |   | в | ΙТ |   |   |     |                              |

|----------|---|---|---|---|---|----|---|---|-----|------------------------------|

| REGISTER | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 | HEX | DESCRIPTION                  |

| INT      | 1 | 1 | х | х | 0 | 0  | 0 | 0 | x0h | Enable Alarm and Int<br>Mode |

NOTE: x indicate other control bits

Once the registers are set, the following waveform will be seen at  $\overline{IRQ}$ :

Note that the status register ALM bit will be set each time the alarm is triggered, but does not need to be read or cleared.

#### Timer Control Register (TMRC) [Address 09h]

#### TABLE 9. TIMER CONTROL REGISTER (TMRC)

| ADDR    | 7   | 6    | 5     | 4     | 3 | 2 | 1     | 0     |

|---------|-----|------|-------|-------|---|---|-------|-------|

| 09h     | ТІМ | TMRE | TMOD1 | TMOD0 | 0 | 0 | TCLK1 | TCLK0 |

| Default | 0   | 0    | 0     | 0     | 0 | 0 | 0     | 0     |

## TIMER CLOCK FREQUENCY SELECTION BITS (TCLK <1:0>)

## For detailed timer operation, please refer to "TIMER COUNTER OPERATION" on page 17.

These bits select the Timer/Watchdog clock frequency for the Timer Counter Register (TCNT, address 13h) and the internal Sub-Timer Counter Register (TSCNT). When the Sub-Timer Initial Register (TSDAT, address 14h) is set to "0", the number of counts changes to the default value. The maximum register value for the TSDAT register is 127 which means the maximum limit for the internal Sub-Timer Counter Register is also 127. See Table 10 for Timer/Watchdog clock frequency selection and the default counts for the Sub-Timer Counter Register.

## TABLE 10. TIMER CLOCK FREQUENCY SELECTION AND DEFAULT VALUE FOR TSDAT REGISTER

| TCLK1 | TCLK0 | FUNCTION   | COMMENT                                                                                                                         |

|-------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | 100Hz/4kHz | 100Hz for TCNT, 4kHz for TSCNT<br>Default Value for TSDAT = 41<br>(41 TSCNT counts = 1ms)<br>(Not available for Watchdog Timer) |

| 0     | 1     | 1sec/100Hz | 1sec for TCNT, 100Hz for TSCNT<br>Default Value for TSDAT = 100<br>(100 TSCNT counts = 1s)                                      |

| 1     | 0     | 1min/1sec  | 1min for TCNT, 1sec for TSCNT<br>Default Value for TSDAT = 60<br>(60 TSCNT counts = 1min)<br>(RTC must be enabled)              |

| 1     | 1     | 1hr/1min   | 1hour for TCNT, 1min for TSCNT<br>Default Value for TSDAT = 60<br>(60 TSCNT counts = 1hr)<br>(RTC must be enabled)              |

The Timer Counter and Sub-Timer Counter Registers advance the counter value based on the frequency or time setting by the TCLK<1:0> bits.

The following are examples of Timer clock frequency selection bits on Timer Counter and Sub-Timer Counter Registers.

Example 1 - TCLK1 is set to "1", TCLK0 is set to "0", and Sub-Timer Initial Register is set to "0". The internal Sub-Timer Counter will increment every 1s. When the internal Sub-Timer Counter reaches to 60, the default value, the Timer Counter will increment by one which means the Timer Counter will increment every one minute.

Example 2- TCLK1 is set to "1", TCLK0 is set to "0", and Sub-Timer Initial Register is set to "10d". The internal Sub-Timer Counter will increment every 1s. When the internal Sub-Timer Counter reaches to 10, the Timer Counter will increment by one which means the Timer Counter will increment every ten seconds.

Example 3- TCLK1 is set to "0", TCLK0 is set to "1", and Sub-Timer Initial Register is set to "0". The internal Sub-Timer Counter will increment every 1ms (100Hz). When the internal Sub-Timer Counter reaches to 100, the default value2, the Timer Counter will increment by one which means the Timer Counter will increment every one second.

#### TIMER FUNCTION SELECTION BITS (TMOD <1:0>)

The Timer interrupt has four different functions:

- 1. Count Down Timer

- 2. Secondary Alarm Timer

- 3. Watchdog Timer

- 4. Power Fail Count-up Timer

Please see Table 11 for Timer counting functions selection.

| TABLE 11. | TIMER COUNTING FUNCTION SELECTION | I |

|-----------|-----------------------------------|---|

|-----------|-----------------------------------|---|

| TMOD1 | TMOD0 | FUNCTION                        | COMMENT                                                                                 |  |  |  |

|-------|-------|---------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| 0     | 0     | Count Down<br>Timer             | Basic count down timer<br>(TCNT register decrement)                                     |  |  |  |

| 0     | 1     | Secondary<br>Alarm Timer        | Basic count down timer activated by<br>ALARM IRQ (ALM bit)<br>(TCNT register decrement) |  |  |  |

| 1     | 0     | Watchdog<br>Timer               | Count up timer with periodic<br>interrupt<br>(TCNT register increment)                  |  |  |  |

| 1     | 1     | Power Fail<br>Count-up<br>Timer | Count up after device entered into<br>battery mode<br>(TCNT register increment)         |  |  |  |

#### TIMER ENABLE BIT (TMRE)

This bit enables/disables the timer function. When the TMRE bit is set to "1", the timer is enabled. To display timer interrupt on the  $\overline{IRQ2}$  pin, the IRQ2E has to be set to "1". When the TMRE bit is cleared to "0", the timer function is disabled. The TMRE bit is set to "0" on power-up.

#### TIMER PULSE/EVENT INTERRUPT BIT (TIM)

This bit enables/disables the interrupt mode of the timer function. When the TIM bit is set to "1", the timer will operate in the interrupt mode. An active low pulse width of 210ms will appear at the IRQ2 pin when the RTC is triggered by the timer as defined by the timer registers (12h to 15h). When the TIM bit is cleared to "0", the timer will operate in standard mode, where the IRQ2 pin will be held low until TMR status bit is cleared to "0". The TIM bit is set to "0" on power-up.

| TIM BIT | TIMER PULSE/EVENT INTERRUPT FUNCTION         |  |  |  |  |  |  |

|---------|----------------------------------------------|--|--|--|--|--|--|

| 0       | Single Time Event Set By Timer               |  |  |  |  |  |  |

| 1       | Repetitive/Recurring Time Event Set By Timer |  |  |  |  |  |  |

## Timer Registers

#### Addresses [12h to 15h]

#### Timer Initial Register (TDAT) [Address 12h]

The Timer Initial Register is located in the memory map at address 12h. This is a volatile register that stores the timer limit for the timer counter register.

| ADDR    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 12h     | TDAT7 | TDAT6 | TDAT5 | TDAT4 | TDAT3 | TDAT2 | TDAT1 | TDAT0 |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Timer Counter Register (TCNT) [Address 13h]

The Timer Counter Register is located in the memory map at address 13h. This is a volatile register that keeps the current timer counter value. This byte is read only.

| ADDR    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 13h     | TCNT7 | TCNT6 | TCNT5 | TCNT4 | TCNT3 | TCNT2 | TCNT1 | TCNT0 |

| Default | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### TABLE 13. TIMER COUNTER REGISTER (TCNT)

#### Sub-Timer Initial Register (TSDAT) [Address 14h]

The Sub-Timer Initial Register is located in the memory map at address 14h. This is a volatile register that stores the timer limit for the internal sub-timer counter register. This byte is write only and only read back a "0"

| TABLE 14  | SUB-TIMER | ΙΝΙΤΙΔΙ | REGISTER      | (TSDAT) |

|-----------|-----------|---------|---------------|---------|

| IADEE 14. |           |         | IN LOID I LIN | (IODAI) |

| ADDR    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| 14h     | TSDAT7 | TSDAT6 | TSDAT5 | TSDAT4 | TSDAT3 | TSDAT2 | TSDAT1 | TSDAT0 |

| Default | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Internal Sub-Timer Counter Register (TSCNT)

The Internal Sub-Timer Counter Register is an internal volatile register that keeps the current sub-timer counter value. This byte is not accessible.

## **Timer Counter Operation**

The ISL12082 timer consists of a timer counter and a sub-timer counter. The timer counter can be an incremental or a decremental counter which depends on the setting of the Timer Function Selection Bits (TMOD[1:0], address 09h, bits 5 and 4). Sub-timer counter works as an incremental counter. The timer counter is represented by the Timer Counter Register (TCNT, address 13h) and the sub-timer counter is represented by the internal Sub-Timer Counter Register (TSCNT) which is not accessible by the user. The Timer Initial Register (TDAT, address 12h) and the Sub-Timer Initial Register (TSDAT, address 14h) are used to set the limit for the TCNT register and internal TSCNT register respectively. The TDAT register must contain a minimum value of 2 in order to operate the timer properly and the TSAT register can be set to any value up to 127 decimal. If the TSDAT register is set to "0", the TSDAT will reset to the default value which depends on the TCLK[1:0] bits setting which is shown in Table 10.

Once the timer function is enabled by setting the TMRE bit to "1", the TCNT register is set to the TDAT value or one depending on the setting of the TMOD[1:0] bits, and the internal TSCNT register is set to one. Then the internal TSCNT will increment one bit at a time and at a frequency set by the Timer Clock Frequency Selection Bits (TCLK[1:0], address 09h bits 1 and 0). The internal TSCNT register will overflow when it counts up to the value in the TSDAT register. If the TSDAT register is set to "0", the internal TSCNT will count up to the default TSDAT register value to overflow. If the internal TSCNT register overflows, the TCNT register will increment or decrement by one depending on the setting of the TMOD[1:0] bits and the internal TSCNT register resets back to "1" and repeats the counting cycle. The timer expires when the TCNT register increments to the TDAT register value or decrements to zero depending on the setting of the TMOD[1:0] bits. The TMR bit is set and the IRQ2 is held low to indicate the timer interrupt. The IRQ2 only activates for the timer interrupt when the IRQ2E (address 8h, bit 3) sets to "1".

There are two timer operation modes for the IRQ2: Single Event and Periodic Interrupt Mode:

• Single Event Mode is enabled by setting the TMRE bit to "1", the TIM bit to "0", and IRQ2E bit to "1". This mode permits a <u>one-time</u> timer counting cycle. Once the timer expires, the TMR status bit is set to "1" and the IRQ2 output will be held low until the TMR status bit is reset to "0". This can be done manually or by using the auto-reset feature. Once the TMR status bit is reset, the timer will reset and restart the counting cycle. If the TMRE bit is set to "0" before the TMR status bit is reset, then counting is halted.

The IRQ2 can be reset by setting the TMRE bit to "0" but the TMR status bit will remain at "1". The timer can be re-enabled with TMR status remaining at "1".

• Periodic Interrupt Mode is enabled by setting the TMRE bit to "1", the TIM bit to "1", and IRQ2E bit to "1". The timer must be disabled prior to setting TIM bit to "1" in order to enable the Periodic Interrupt Mode. In the Periodic Interrupt Mode, the IRQ2 output will be pulsed <u>each time</u> a timer expires. The low and the high pulse width of the IRQ2 can be calculated by the TCLK[1:0] bits, the TDAT register and the TSDAT register. After the interrupt, the internal TSCNT register will keep counting until it overflows. When the internal TSCNT register overflows, the IRQ2 pin is pulled high and the TSCNT register is reset to the value in TDAT register or "1" depended on the TMOD[1:0] setting. Then the new counting cycle begins.

The TMR bit is still set each time when the timer expired. Resetting the TMR status bit to "0" from "1" in the Periodic Interrupt Mode will cause the TCNT register and the internal TSCNT register to reset. Depending on when the TMR bit is being reset, the low pulse width or the high pulse width will be prolonged for the amount of time the counter has counted.

The Interrupt Mode can be disabled by setting the TIM bit to "0" when timer is enabled. The interrupt mode can not be enabled after the timer is enabled.

When the timer is disabled by setting the TMRE bit to "0", the register value for the timer counter and the sub-timer are set back to the default value. The default value for the Timer Counter Register (TCNT, address 13h) is "0" and Sub-Timer Counter Register (TSCNT, address 15h) is "1".

Following are the detailed descriptions of the four different timer modes.

#### Count Down Timer

The Count Down timer is a basic countdown timer. Once the timer is enabled by setting TMRE bit to "1", the TCNT register is set to the value in TDAT register. The TDAT register must have a value of two or greater in order for the timer to start. If the timer is enabled with TDAT register less than two, then the timer is disabled and the TDAT register has to be set to an appropriate value before the timer can be enabled again. The internal TSCNT register increments from one, and the incremental frequency is set by the TCLK[1:0] bits. Once the internal TSCNT register overflows, the TCNT register will decrement by one and the internal TSCNT register will reset back to one and start counting again until the TCNT register reaches zero. Once the TCNT register reaches zero, the timer will issue an interrupt that will set the TMR status bit to "1" and set the IRQ2 pin to low (if IRQ2E bit is set to "1").

When the TIM = "0" (single event mode), the timer stops after the timer expires. The timer will restart and the IRQ2 pin will be high when the TMR bit is cleared to "0". The timer can also be restarted by resetting the TMRE bit to "1" after setting it to "0". This method is not recommended since the TMR status will not clear by this method and may cause confusion in the system. In single event mode, the time interval for the timer expiration is calculated by using Equation 3.

Timer Interval = TDAT\*TSDAT\*TCLK (EQ. 3)

Where, TDAT is the value in the TDAT register. TSDAT is the value in the TSDAT register (use default if 0). TCLK is the period set by the TCLK[1:0] bits. For 4kHz setting, please use  $244\mu$ s for the period. For 100Hz setting please use 10ms for the period.

When the TIM = "1" (periodic interrupt mode), the timer repeats the countdown function automatically after the timer expires. The periodic interrupt function can only be monitored on the IRQ2 pin; therefore, the IRQ2E bit must be set to "1" to show timer interrupt on the IRQ2 pin. The IRQ2 pin is pulsed each time the timer expires. Once the timer expires, the TMR status bit set to "1" and the IRQ2 pin goes low. The internal TSCNT register will reset and continue counting. Once the internal TSCNT overflows after the timer expires, the IRQ2 pin will pull back to high but the TMR status bit will remain at "1" until the user clears it. The TCNT register will reset back to the value in the TDAT register to start the new count cycle. The timer will continue counting until the TMRE = "0" to disable the timer. In periodic interrupt mode, the time interval for the timer expiration is calculated differently for the first timer expiration and for the next and succeeding timer expiration. For the first timer expiration, the time interval is calculated by using Equation 3. For the next

and succeeding timer expiration, the time interval can be treated as the high pulse width of  $\overline{IRQ2}$  pin ( $T_{HIGH\_CDT}$ ), and it is calculated by using Equation 4. The low interrupt pulse width of  $\overline{IRQ2}$  pin ( $T_{LOW\_CDT}$ ) is calculated by using Equation 5. Since the TMR status bit is not reset automatically by the device at the new count cycle, if the user resets it, the timer will reset and the next count cycle will be seen as the first count cycle by the device.

$T_{HIGH CDT} = (TDAT-1)^*TSDAT^*TCLK$  (EQ. 4)

Where, TDAT is the value in the TDAT register. TSDAT is the value in the TSDAT register (use default if 0). TCLK is the period set by the TCLK[1:0] bits. For 4kHz setting, please use  $244\mu$ s for the period. For 100Hz setting please use 10ms for the period.

$T_{LOW CDT} = TSDAT^{TCLK}$  (EQ. 5)

Where, TSDAT is the value in the TSDAT register (use default if 0). TCLK is the period set by the TCLK[1:0] bits. For 4kHz setting, please use 244µs for the period. For 100Hz setting please use 10ms for the period.