June 2002 Revised June 2002

# **FIN1026**

# 3.3V LVDS 2-Bit High Speed Differential Receiver

### **General Description**

This dual receiver is designed for high speed interconnects utilizing Low Voltage Differential Signaling (LVDS) technology. The receiver translates LVDS levels, with a typical differential input threshold of 100mV, to LVTTL signal levels. LVDS provides low EMI at ultra low power dissipation even at high frequencies. This device is ideal for high speed transfer of clock and data.

The FIN1026 can be paired with its companion driver, the FIN1025, or any other LVDS driver.

### **Features**

- Greater than 400Mbs data rate

- Flow-through pinout simplifies PCB layout

- 3.3V power supply operation

- 0.4ns maximum differential pulse skew

- 2.5ns maximum propagation delay

- Low power dissipation

- Power-Off protection

- Fail safe protection for open-circuit, shorted and terminated non-driven input conditions

- Meets or exceeds the TIA/EIA-644 LVDS standard

- 14-Lead TSSOP package saves space

### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------|--|--|--|

| FIN1026MTC   | MTC14          | 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

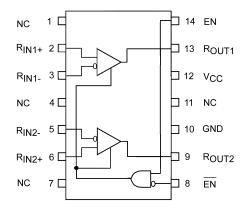

# **Connection Diagram**

# **Pin Descriptions**

| Pin Name                              | Description                 |  |  |

|---------------------------------------|-----------------------------|--|--|

| R <sub>OUT1</sub> , R <sub>OUT2</sub> | LVTTL Data Outputs          |  |  |

| $R_{IN1+}, R_{IN2+}$                  | Non-Inverting LVDS Inputs   |  |  |

| R <sub>IN1-</sub> , R <sub>IN2-</sub> | Inverting LVDS Inputs       |  |  |

| EN                                    | Driver Enable Pin           |  |  |

| EN                                    | Inverting Driver Enable Pin |  |  |

| V <sub>CC</sub>                       | Power Supply                |  |  |

| GND                                   | Ground                      |  |  |

| NC                                    | No Connect                  |  |  |

### **Truth Table**

|           | Outputs   |                     |                   |                  |  |

|-----------|-----------|---------------------|-------------------|------------------|--|

| EN        | EN        | R <sub>IN+</sub>    | R <sub>IN</sub> _ | R <sub>OUT</sub> |  |

| Н         | L or Open | Н                   | L                 | Н                |  |

| Н         | L or Open | L                   | Н                 | L                |  |

| Н         | L or Open | Fail Safe Condition |                   | Н                |  |

| Х         | Н         | Х                   | Х                 | Z                |  |

| L or Open | Х         | Х                   | Х                 | Z                |  |

- H = HIGH Logic Level L = LOW Logic Level

- X = Don't Care

- Z = High Impedance

- Fail Safe = Open, Shorted, Terminated

# **Absolute Maximum Ratings**(Note 1)

# $\begin{array}{lll} \mbox{Supply Voltage (V$_{CC}$)} & -0.5\mbox{V to } +4.6\mbox{V} \\ \mbox{LVDS DC Input Voltage (V$_{IN}$)} & -0.5\mbox{V to } +4.6\mbox{V} \\ \mbox{LVTTL DC Input Voltage (V$_{IN}$)} & -0.5\mbox{V to } 6\mbox{V} \end{array}$

$\begin{array}{lll} \mbox{DC Output Voltage (V_{OUT})} & -0.5 \mbox{V to 6V} \\ \mbox{DC Output Current (I}_{\mbox{O}}) & 16 \mbox{mA} \\ \mbox{Storage Temperature Range (T_{STG})} & -65 \mbox{°C to +150 °C} \\ \end{array}$

$\label{eq:max_Junction} \begin{aligned} &\text{Max Junction Temperature } (T_J) \\ &\text{Lead Temperature } (T_L) \end{aligned}$

(Soldering, 10 seconds) 260°C

ESD (Human Body Model) 10,000V

ESD (Machine Model) 600V

# Recommended Operating Conditions

Supply Voltage (V<sub>CC</sub>) 3.0V to 3.6V

Magnitude of Differential Voltage

$\begin{array}{ccc} (|V_{ID}|) & 100 \text{mV to } V_{CC} \\ \text{Common-Mode Input Voltage } (V_{IC}) & 0.05 \text{V to } 2.35 \text{V} \\ \text{Input Voltage } (V_{IN}) & 0 \text{ to } V_{CC} \\ \text{Operating Temperature } (T_{A}) & -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C} \\ \end{array}$

Note 1: The "Absolute Maximum Ratings": are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature and output/input loading variables. Fairchild does not recommend operation of circuits outside databook specification.

### **DC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified

| Symbol              | Parameter                         | Test Conditions                                                | Min                  | Typ<br>(Note 2) | Max  | Units |

|---------------------|-----------------------------------|----------------------------------------------------------------|----------------------|-----------------|------|-------|

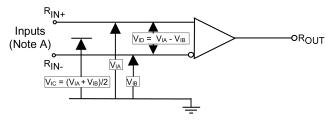

| V <sub>TH</sub>     | Differential Input Threshold HIGH | See Figure 1, V <sub>IC</sub> = +0.05V, +1.2V, or 2.35V        |                      |                 | 100  | mV    |

| V <sub>TL</sub>     | Differential Input Threshold LOW  | See Figure 1, V <sub>IC</sub> = +0.05V, +1.2V, or 2.35V        | -100                 |                 |      | mV    |

| I <sub>IN</sub>     | Input Current                     | V <sub>IN</sub> = 0V or V <sub>CC</sub>                        |                      |                 | ±20  | μΑ    |

| I <sub>I(OFF)</sub> | Power-Off Input Current           | V <sub>CC</sub> = 0V, V <sub>IN</sub> = 0V or 3.6V             |                      |                 | ±20  | μΑ    |

| V <sub>OH</sub>     | Output HIGH Voltage               | $I_{OH} = -100 \mu A$                                          | V <sub>CC</sub> -0.2 | 3.29            |      | V     |

|                     |                                   | I <sub>OH</sub> = -8 mA                                        | 2.4                  | 3.1             |      |       |

| V <sub>OL</sub>     | Output LOW Voltage                | I <sub>OH</sub> = 100 μA                                       |                      | 0               | 0.2  | V     |

|                     |                                   | I <sub>OL</sub> = 8 mA                                         |                      | 0.18            | 0.5  | ı v   |

| l <sub>OZ</sub>     | Disabled Output Leakage Current   | EN = 0.8 and EN* = 2V, V <sub>OUT</sub> = 3.6V or 0V           |                      |                 | ±20  | μΑ    |

| V <sub>IK</sub>     | Input Clamp Voltage               | I <sub>IK</sub> = -18 mA                                       | -1.5                 | -0.8            |      | V     |

| los                 | Output Short Circuit Current      | Receiver Enabled, V <sub>OUT</sub> = 0V                        | -15                  |                 | -100 | mA    |

|                     |                                   | (one output shorted at a time)                                 |                      |                 |      |       |

| I <sub>CCZ</sub>    | Disabled Power Supply Current     | Receiver Disabled                                              |                      | 2.6             | 5    | mA    |

| Icc                 | Power Supply Current              | Receiver Enabled, $(R_{IN+} = 1V \text{ and } R_{IN-} = 1.4V)$ |                      | 4.8             | 8.5  | mA    |

|                     |                                   | or ( $R_{IN+} = 1.4V$ and $R_{IN-} = 1V$ )                     |                      | 4.0             | 0.5  | IIIA  |

150°C

**Note 2:** All typical values are at  $T_A = 25^{\circ}\text{C}$  and with  $V_{CC} = 3.3\text{V}$ .

### **AC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified

| Symbol              | Parameter                                       | Test Conditions                                  | Min | Typ<br>(Note 3) | Max | Units |

|---------------------|-------------------------------------------------|--------------------------------------------------|-----|-----------------|-----|-------|

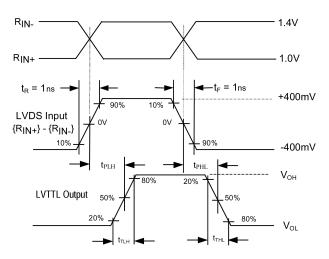

| t <sub>PLH</sub>    | Propagation Delay LOW-to-HIGH                   |                                                  | 1.0 |                 | 2.5 | ns    |

| t <sub>PHL</sub>    | Propagation Delay HIGH-to-LOW                   |                                                  | 1.0 |                 | 2.5 | ns    |

| t <sub>TLH</sub>    | Output Rise Time (20% to 80%)                   |                                                  |     | 0.7             | 1.2 | ns    |

| t <sub>THL</sub>    | Output Fall Time (80% to 20%)                   | $ V_{ID}  = 400 \text{ mV}, C_L = 10 \text{ pF}$ |     | 0.7             | 1.2 | ns    |

| t <sub>SK(P)</sub>  | Pulse Skew  t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 1 and Figure 2                        |     |                 | 0.4 | ns    |

| t <sub>SK(LH)</sub> | Channel-to-Channel Skew                         |                                                  |     |                 | 0.3 | ns    |

| t <sub>SK(HL)</sub> | (Note 4)                                        |                                                  |     |                 | 0.3 | 115   |

| t <sub>SK(PP)</sub> | Part-to-Part Skew (Note 5)                      |                                                  |     |                 | 1.0 | ns    |

| f <sub>MAX</sub>    | Maximum Operating Frequency (Note 6)            |                                                  | 200 | 375             |     | MHz   |

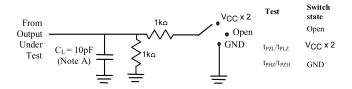

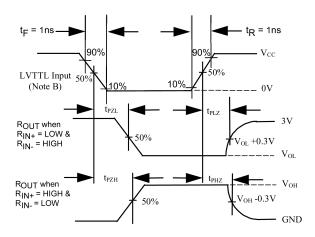

| t <sub>PZH</sub>    | LVTTL Output Enable Time from Z to HIGH         |                                                  |     |                 | 6.0 | ns    |

| t <sub>PZL</sub>    | LVTTL Output Enable Time from Z to LOW          | $R_L = 1k\Omega$ , $C_L = 10 pF$ ,               |     |                 | 6.0 | ns    |

| t <sub>PHZ</sub>    | LVTTL Output Disable Time from HIGH to Z        | See Figure 3                                     |     |                 | 6.0 | ns    |

| t <sub>PLZ</sub>    | LVTTL Output Disable Time from LOW to Z         |                                                  |     |                 | 6.0 | ns    |

| C <sub>IN</sub>     | Input Capacitance                               | Enable Inputs                                    |     | 3.0             |     | pF    |

|                     |                                                 | R <sub>IN</sub> Inputs                           |     | 4.2             |     | PF    |

| C <sub>OUT</sub>    | Output Capacitance                              |                                                  |     | 6               |     | pF    |

Note 3: All typical values are at  $T_A = 25^{\circ}C$  and with  $V_{CC} = 3.3V$ .

Note 4: t<sub>SK(LH)</sub>, t<sub>SK(HL)</sub> is the skew between specified outputs of a single device when the outputs have identical loads and are switching in the same direction.

Note 5:  $t_{SK(PP)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices switching in the same direction (either LOW-to-HIGH or HIGH-to-LOW) when both devices operate with the same supply voltage, same temperature, and have identical test circuits.

Note 6:  $f_{MAX}$  Criteria: Input  $t_R = t_F < 1$  ns,  $V_{ID} = 300$  mV, (1.05V to 1.35V pp), 50% duty cycle; Output duty cycle 40% to 60%,  $V_{OL} < 0.5$ V,  $V_{OH} > 2.4$ V. All channels switching in phase.

Note A: All differential input pulses have frequency = 10MHz,  $t_{R}$  or  $t_{F}$  = 1ns

FIGURE 1. Differential Receiver Voltage Definitions

FIGURE 2. LVDS Input to LVTTL Output AC Waveforms

### **Test Circuit for LVTTL Outputs**

### Voltage Waveforms Enable and Disable Times

FIGURE 3. LVTTL Outputs Test Circuit and AC Waveforms

### Physical Dimensions inches (millimeters) unless otherwise noted -A-0.43 TYP 7.72 4 16 6.4 -B-3.2 0.65 0.2 C B A ALL LEAD TIPS LAND PATTERN RECOMMENDATION PIN #1 IDENT SEE DETAIL A ALL LEAD TIPS 0.90 +0.15 1.2 MAX 0.09-0.20 -C-0.10±0.05 0.65 12.00° TOP & BOTTOM ⊕ 0.13 M A B S C S B0.09 MIN GAGE PLANE NOTES: 0.25 A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AB, REF NOTE 6, DATE 7/93. B. DIMENSIONS ARE IN MILLIMETERS. C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND 0.6 ±0.1 SEATING PLANE TIE BAR EXTRUSIONS. D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1982. -- 1 00-R0.09 MIN

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC14

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

MTC14RevC3

A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**DETAIL A**

www.fairchildsemi.com