## **FM1608B (PDIP)**

## 64Kb Bytewide 5V F-RAM Memory

#### **Features**

#### 64Kbit Ferroelectric Nonvolatile RAM

- Organized as 8,192 x 8 bits

- High Endurance 1 Trillion (10<sup>12</sup>) Read/Writes

- 38 year Data Retention @ +75°C

- NoDelay<sup>TM</sup> Writes

- Advanced High-Reliability Ferroelectric Process

#### **Superior to BBSRAM Modules**

- No Battery Concerns

- Monolithic Reliability

- Superior for Moisture, Shock, and Vibration

- Resistant to Negative Voltage Undershoots

## **SRAM & EEPROM Compatible**

- JEDEC 8Kx8 SRAM & EEPROM pinout

- 70 ns Access Time

- 130 ns Cycle Time

### **Low Power Operation**

- 15 mA Active Current

- 25 μA (typ.) Standby Current

#### **Industry Standard Configuration**

- Extended Temperature 0°C to +85°C

- 28-pin "Green"/RoHS PDIP Package

## **Description**

The FM1608B is a 64-kilobit nonvolatile memory employing an advanced ferroelectric process. A ferroelectric random access memory or F-RAM is nonvolatile but operates in other respects as a RAM. It provides data retention for 38 years while eliminating the reliability concerns, functional disadvantages and system design complexities of battery-backed SRAM (BBSRAM). Fast write timing and high write endurance make F-RAM superior to other types of nonvolatile memory.

In-system operation of the FM1608B is very similar to other RAM devices. Minimum read- and write-cycle times are equal. The F-RAM memory, however, is nonvolatile due to its unique ferroelectric memory process. Unlike BBSRAM, the FM1608B is a truly monolithic nonvolatile memory. It provides the same functional benefits of a fast write without the disadvantages associated with modules and batteries or hybrid memory solutions.

These capabilities make the FM1608B ideal for nonvolatile memory applications requiring frequent or rapid writes in a bytewide environment. The availability of a through-hole package allows ease of insertion and removal in systems that utilize a DIP socket. Device specifications are guaranteed over the extended temperature range of 0°C to +85°C.

## **Pin Configuration**

| Ordering Information |                          |  |

|----------------------|--------------------------|--|

| FM1608B-PG           | 28-pin "Green"/RoHS PDIP |  |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

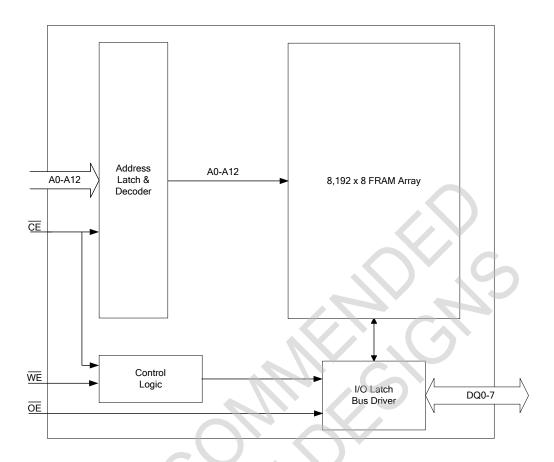

Figure 1. Block Diagram

#### **Pin Description**

| Pin Name | Type   | Description                                                                        |

|----------|--------|------------------------------------------------------------------------------------|

| A(12:0)  | Input  | Address: The 13 address lines select one of 8,192 bytes in the F-RAM array. The    |

|          |        | address value is latched on the falling edge of /CE.                               |

| DQ(7:0)  | I/O    | Data: 8-bit bi-directional data bus for accessing the F-RAM array.                 |

| /CE      | Input  | Chip Enable: /CE selects the device when low. Asserting /CE low causes the         |

|          |        | address to be latched internally. Address changes that occur after /CE goes low    |

|          |        | will be ignored until the next falling edge occurs.                                |

| /OE      | Input  | Output Enable: Asserting /OE low causes the FM1608B to drive the data bus when     |

|          |        | valid data is available. Deasserting /OE high causes the DQ pins to be tri-stated. |

| /WE      | Input  | Write Enable: Asserting /WE low causes the FM1608B to write the contents of the    |

| Ť        |        | data bus to the address location latched by the falling edge of /CE.               |

| VDD      | Supply | Supply Voltage: 5V                                                                 |

| VSS      | Supply | Ground                                                                             |

### **Functional Truth Table**

| /CE          | /WE      | Function                                   |

|--------------|----------|--------------------------------------------|

| Н            | X        | Standby/Precharge                          |

| $\downarrow$ | X        | Latch Address (and Begin Write if /WE=low) |

| L            | Н        | Read                                       |

| L            | <b>↓</b> | Write                                      |

Note: The /OE pin controls only the DQ output buffers.

#### Overview

The FM1608B is a bytewide F-RAM memory. The memory array is logically organized as 8,192 x 8 and is accessed using an industry standard parallel interface. All data written to the part is immediately nonvolatile with no delay. Functional operation of the F-RAM memory is the same as SRAM type devices, except the FM1608B requires a falling edge of /CE to start each memory cycle.

### **Memory Architecture**

Users access 8,192 memory locations each with 8 data bits through a parallel interface. The complete 13-bit address specifies each of the 8,192 bytes uniquely. Internally, the memory array is organized into 1024 rows of 8-bytes each. This row segmentation has no effect on operation, however the user may wish to group data into blocks by its endurance characteristics as explained on page 4.

The cycle time is the same for read and write memory operations. This simplifies memory controller logic and timing circuits. Likewise the access time is the same for read and write memory operations. When /CE is deasserted high, a precharge operation begins, and is required of every memory cycle. Thus unlike SRAM, the access and cycle times are not equal. Writes occur immediately at the end of the access with no delay. Unlike an EEPROM, it is not necessary to poll the device for a ready condition since writes occur at bus speed.

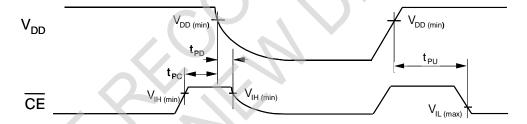

It is the user's responsibility to ensure that VDD remains within datasheet tolerances to prevent incorrect operation. Also proper voltage level and timing relationships between VDD and /CE must be maintained during power-up and power-down events. See Power Cycle Timing diagram on page 9.

## **Memory Operation**

The FM1608B is designed to operate in a manner similar to other bytewide memory products. For users familiar with BBSRAM, the performance is comparable but the bytewide interface operates in a slightly different manner as described below. For users familiar with EEPROM, the obvious differences result from the higher write performance of F-RAM technology including NoDelay writes and much higher write endurance.

### **Read Operation**

A read operation begins on the falling edge of /CE. At this time, the address bits are latched and a memory cycle is initiated. Once started, a full

memory cycle must be completed internally even if /CE goes inactive. Data becomes available on the bus after the access time has been satisfied.

After the address has been latched, the address value may be changed upon satisfying the hold time parameter. Unlike an SRAM, changing address values will have no effect on the memory operation after the address is latched.

The FM1608B will drive the data bus when /OE is asserted low. If /OE is asserted after the memory access time has been satisfied, the data bus will be driven with valid data. If /OE is asserted prior to completion of the memory access, the data bus will not be driven until valid data is available. This feature minimizes supply current in the system by eliminating transients caused by invalid data being driven onto the bus. When /OE is inactive the data bus will remain tri-stated.

#### **Write Operation**

Writes occur in the FM1608B in the same time interval as reads. The FM1608B supports both /CE-and /WE-controlled write cycles. In all cases, the address is latched on the falling edge of /CE.

In a /CE controlled write, the /WE signal is asserted prior to beginning the memory cycle. That is, /WE is low when /CE falls. In this case, the part begins the memory cycle as a write. The FM1608B will not drive the data bus regardless of the state of /OE.

In a /WE controlled write, the memory cycle begins on the falling edge of /CE. The /WE signal falls after the falling edge of /CE. Therefore, the memory cycle begins as a read. The data bus will be driven according to the state of /OE until /WE falls. The timing of both /CE- and /WE-controlled write cycles is shown in the electrical specifications.

Write access to the array begins asynchronously after the memory cycle is initiated. The write access terminates on the rising edge of /WE or /CE, whichever is first. Data set-up time, as shown in the electrical specifications, indicates the interval during which data cannot change prior to the end of the write access.

Unlike other truly nonvolatile memory technologies, there is no write delay with F-RAM. Since the read and write access times of the underlying memory are the same, the user experiences no delay through the bus. The entire memory operation occurs in a single bus cycle. Therefore, any operation including read or write can occur immediately following a write. Data

polling, a technique used with EEPROMs to determine if a write is complete, is unnecessary.

### **Precharge Operation**

The precharge operation is an internal condition that prepares the memory for a new access. All memory cycles consist of a memory access and a precharge. The precharge is initiated by deasserting the /CE pin high. It must remain high for at least the minimum precharge time  $t_{\rm PC}$ .

The user determines the beginning of this operation since a precharge will not begin until /CE rises. However, the device has a maximum /CE low time specification that must be satisfied.

#### **Endurance**

Internally, a F-RAM operates with a read and restore mechanism. Therefore, each read and write cycle involves a change of state. The memory architecture is based on an array of rows and columns. Each read or write access causes an endurance cycle for an entire row. In the FM1608B, a row is 64 bits wide. Every 8-byte boundary marks the beginning of a new row. Endurance can be optimized by ensuring frequently accessed data is located in different rows. Regardless, F-RAM offers substantially higher write endurance than other nonvolatile memories. The rated endurance limit of  $10^{12}$  cycles will allow 3,000

accesses per second to the same row for over 10 years.

### **F-RAM Design Considerations**

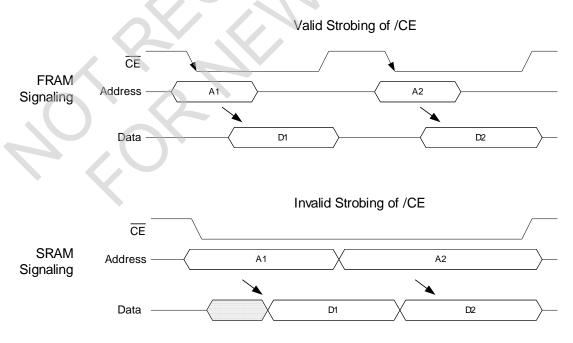

When designing with F-RAM for the first time, users of SRAM will recognize a few minor differences. First, bytewide F-RAM memories latch each address on the falling edge of chip enable. This allows the address bus to change after starting the memory access. Since every access latches the memory address on the falling edge of /CE, users cannot ground it as they might with SRAM.

Users who are modifying existing designs to use F-RAM should examine the memory controller for timing compatibility of address and control pins. Each memory access must be qualified with a low transition of /CE. In many cases, this is the only change required. An example of the signal relationships is shown in Figure 2 below. Also shown is a common SRAM signal relationship that will not work for the FM1608B.

The reason for /CE to strobe for each address is two-fold: it latches the new address and creates the necessary precharge period while /CE is high.

Figure 2. Chip Enable and Memory Address Relationships

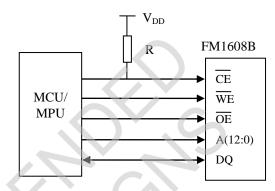

A second design consideration relates to the level of  $V_{DD}$  during operation. Battery-backed SRAMs are forced to monitor  $V_{DD}$  in order to switch to battery backup. They typically block user access below a certain  $V_{DD}$  level in order to prevent loading the battery with current demand from an active SRAM. The user can be abruptly cut off from access to the nonvolatile memory in a power down situation with no warning or indication.

F-RAM memories do not need this system overhead. The memory will not block access at any  $V_{DD}$  level that complies with the specified operating range. The user should take measures to prevent the processor from accessing memory when  $V_{DD}$  is out-of-tolerance. The common design practice of holding a processor in reset during powerdown may be sufficient. It is recommended that Chip Enable is pulled high and allowed to track  $V_{DD}$  during powerup and powerdown cycles. It is the user's responsibility to ensure that chip enable is high to prevent accesses

below  $V_{DD}$  min. (4.5V). Figure 3 shows a pullup resistor on /CE which will keep the pin high during power cycles assuming the MCU/MPU pin tri-states during the reset condition. The pullup resistor value should be chosen to ensure the /CE pin tracks  $V_{DD}$  yet a high enough value that the current drawn when /CE is low is not an issue.

Figure 3. Use of Pullup Resistor on /CE

## **Electrical Specifications**

**Absolute Maximum Ratings**

| Symbol             | Description                                          | Ratings                      |

|--------------------|------------------------------------------------------|------------------------------|

| $V_{\mathrm{DD}}$  | Power Supply Voltage with respect to V <sub>SS</sub> | -1.0V to +7.0V               |

| $ m V_{IN}$        | Voltage on any pin with respect to V <sub>SS</sub>   | -1.0V to +7.0V               |

|                    |                                                      | and $V_{IN} < V_{DD} + 1.0V$ |

| $T_{STG}$          | Storage Temperature                                  | -55°C to + 125°C             |

| $T_{LEAD}$         | Lead Temperature (Soldering, 10 seconds)             | 260°C                        |

| $V_{\mathrm{ESD}}$ | Electrostatic Discharge Voltage                      |                              |

|                    | - Human Body Model (AEC-Q100-002 Rev. E)             | 4kV                          |

|                    | - Charged Device Model (AEC-Q100-011 Rev. B)         | 1.25kV                       |

|                    | - Machine Model (AEC-Q100-003 Rev. E)                | 300V                         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only, and the functional operation of the device at these or any other conditions above those listed in the operational section of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

**DC Operating Conditions** ( $T_A = 0$ °C to + 85°C,  $V_{DD} = 4.5$ V to 5.5V unless otherwise specified)

| Symbol    | Parameter                                     | Min           | Тур | Max            | Units | Notes |

|-----------|-----------------------------------------------|---------------|-----|----------------|-------|-------|

| $V_{DD}$  | Power Supply                                  | 4.5           | 5.0 | 5.5            | V     |       |

| $I_{DD}$  | V <sub>DD</sub> Supply Current                |               |     | 15             | mA    | 1     |

| $I_{SB1}$ | Standby Current (TTL)                         |               | -   | 1.8            | mA    | 2     |

| $I_{SB2}$ | Standby Current (CMOS )                       |               | 25  | 50             | μΑ    | 3     |

| $I_{LI}$  | Input Leakage Current                         | -             |     | ±1             | μΑ    | 4     |

| $I_{LO}$  | Output Leakage Current                        |               |     | ±1             | μΑ    | 4     |

| $V_{IH}$  | Input High Voltage                            | 2.0           |     | $V_{DD} + 0.3$ | V     |       |

| $V_{IL}$  | Input Low Voltage                             | -0.3          |     | 0.8            | V     |       |

| $V_{OH1}$ | Output High Voltage (I <sub>OH</sub> = -2 mA) | 2.4           |     |                | V     |       |

| $V_{OH2}$ | Output High Voltage ( $I_{OH} = -100 \mu A$ ) | $V_{DD}$ -0.2 |     |                | V     |       |

| $V_{OL1}$ | Output Low Voltage (I <sub>OL</sub> = 4.2 mA) |               |     | 0.4            | V     |       |

| $V_{OL2}$ | Output Low Voltage ( $I_{OL} = 150 \mu A$ )   |               |     | 0.2            | V     |       |

#### Notes

- 1.  $V_{DD} = 5.5V$ , /CE cycling at minimum cycle time. All inputs at CMOS levels, all outputs unloaded.

- 2.  $V_{DD} = 5.5V$ , /CE at  $V_{IH}$ , All other pins at TTL levels.

- 3.  $V_{DD} = 5.5V$ , /CE at  $V_{IH}$ , All other pins at CMOS levels (0.2V or  $V_{DD}$ -0.2V).

- 4.  $V_{IN}$ ,  $V_{OUT}$  between  $V_{DD}$  and  $V_{SS}$ .

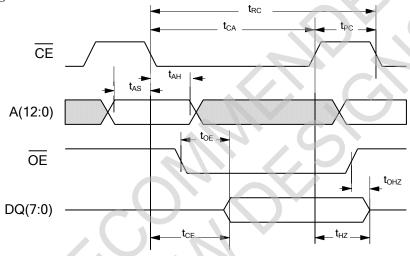

**Read Cycle AC Parameters** ( $T_A = 0$ °C to + 85°C,  $V_{DD} = 4.5$ V to 5.5V unless otherwise specified)

| Symbol           | Parameter                               | Min | Max | Units | Notes |

|------------------|-----------------------------------------|-----|-----|-------|-------|

| $t_{CE}$         | Chip Enable Access Time (to data valid) |     | 70  | ns    |       |

| $t_{CA}$         | Chip Enable Active Time                 | 70  |     | ns    |       |

| $t_{RC}$         | Read Cycle Time                         | 130 |     | ns    |       |

| $t_{PC}$         | Precharge Time                          | 60  |     | ns    |       |

| $t_{AS}$         | Address Setup Time                      | 0   |     | ns    |       |

| $t_{AH}$         | Address Hold Time                       | 15  |     | ns    |       |

| $t_{OE}$         | Output Enable Access Time               |     | 12  | ns    |       |

| $t_{\rm HZ}$     | Chip Enable to Output High-Z            |     | 15  | ns    | 1     |

| t <sub>OHZ</sub> | Output Enable to Output High-Z          |     | 15  | ns    | 1     |

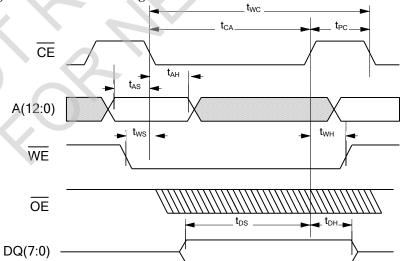

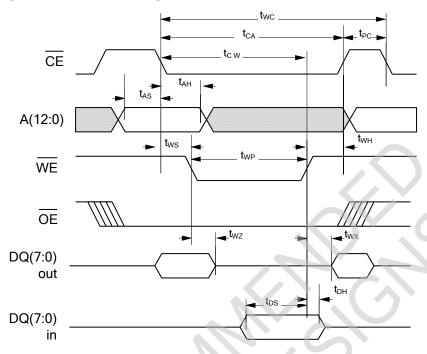

Write Cycle AC Parameters ( $T_A = 0$ °C to + 85°C,  $V_{DD} = 4.5$ V to 5.5V unless otherwise specified)

| Symbol            | Parameter                          | Min | Max | Units | Notes |

|-------------------|------------------------------------|-----|-----|-------|-------|

| $t_{CA}$          | Chip Enable Active Time            | 70  |     | ns    |       |

| $t_{CW}$          | Chip Enable to Write High          | 70  |     | ns    |       |

| $t_{WC}$          | Write Cycle Time                   | 130 |     | ns    |       |

| $t_{PC}$          | Precharge Time                     | 60  |     | ns    |       |

| $t_{AS}$          | Address Setup Time                 | 0   |     | ns    |       |

| $t_{AH}$          | Address Hold Time                  | 15  |     | ns    |       |

| $t_{\mathrm{WP}}$ | Write Enable Pulse Width           | 40  |     | ns    |       |

| $t_{DS}$          | Data Setup                         | 30  | _   | ns    |       |

| $t_{DH}$          | Data Hold                          | 0   |     | ns    |       |

| $t_{ m WZ}$       | Write Enable Low to Output High Z  |     | 15  | ns    | 1     |

| $t_{WX}$          | Write Enable High to Output Driven | 10  |     | ns    | 1     |

| $t_{\rm HZ}$      | Chip Enable to Output High-Z       |     | 15  | ns    | 1     |

| $t_{WS}$          | Write Enable Setup                 | 0   |     | ns    | 2     |

| $t_{ m WH}$       | Write Enable Hold                  | 0   |     | ns    | 2     |

#### Notes

- 1 This parameter is periodically sampled and not 100% tested.

- 2 The relationship between /CE and /WE determines if a /CE- or /WE-controlled write occurs. There is no timing specification associated with this relationship.

**Data Retention**  $(T_A = 0^{\circ}C \text{ to } + 85^{\circ}C)$

| Symbol   | Parameter | Min | Max | Units | Notes |

|----------|-----------|-----|-----|-------|-------|

| $T_{DR}$ | @ +85°C   | 10  | -   | Years |       |

|          | @ +80°C   | 19  | -   | Years |       |

|          | @ +75°C   | 38  | -   | Years |       |

Capacitance ( $T_A = 25$ °C, f=1.0 MHz,  $V_{DD} = 5V$ )

| Symbol    | Parameter                     | Min | Max | Units | Notes |

|-----------|-------------------------------|-----|-----|-------|-------|

| $C_{I/O}$ | Input/Output Capacitance (DQ) | -   | 8   | pF    |       |

| $C_{IN}$  | Input Capacitance             | 1   | 6   | pF    |       |

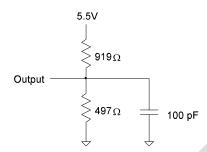

### **AC Test Conditions**

Input Pulse Levels 0 to 3V Input rise and fall times 10 ns Input and output timing levels 1.5V

## **Equivalent AC Load Circuit**

## **Read Cycle Timing**

## Write Cycle Timing - /CE Controlled Timing

## Write Cycle Timing - /WE Controlled Timing

## **Power Cycle Timing**

**Power Cycle Timing** ( $T_A = 0$ °C to + 85°C,  $V_{DD} = 4.5$ V to 5.5V unless otherwise specified)

| Symbol      | Parameter                                     | Min | Max | Units | Notes |

|-------------|-----------------------------------------------|-----|-----|-------|-------|

| $t_{PU}$    | V <sub>DD</sub> (min) to First Access Start   | 10  | -   | ms    | 2     |

| $t_{PD}$    | Last Access Complete to V <sub>DD</sub> (min) | 0   | -   | μs    |       |

| $t_{VR}$    | V <sub>DD</sub> Rise Time                     | 30  | -   | μs/V  | 1,2   |

| $t_{ m VF}$ | V <sub>DD</sub> Fall Time                     | 30  | -   | μs/V  | 1,2   |

#### Notes

- Slope measured at any point on  $V_{\text{DD}}$  waveform. This parameter has been characterized and not 100% tested at 0°C.

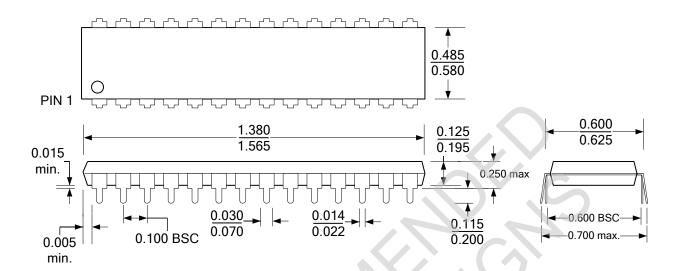

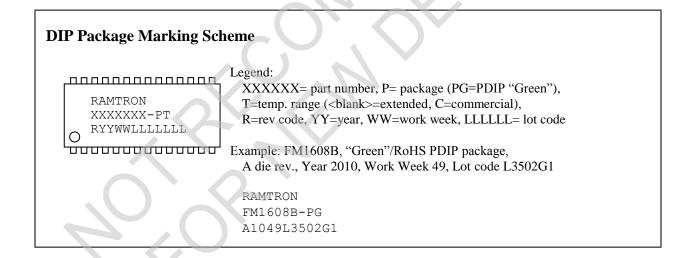

### 28-pin DIP (JEDEC MS-011)

All dimensions in inches

## **Revision History**

| Revision | Date       | Summary                                                                                                                             |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 12/29/2010 | Initial Release                                                                                                                     |

| 1.1      | 2/22/2011  | Changed to commercial temp range. Changed $t_{PU}$ and $t_{VF}$ spec limits. Updated package marking.                               |

| 1.2      | 3/10/2011  | Changed operating temperature to 0C to +85C. Removed "C" from part marking. Added more temperature entries in data retention table. |

| 2.0      | 1/6/2012   | Changed to Pre-Production status. Changed t <sub>VF</sub> spec.                                                                     |

# **Document History**

Document Title: FM1608B (PDIP) 64Kb Bytewide 5V F-RAM Memory Document Number: 001-86599

| Revision | ECN     | Orig. of<br>Change | Submissio<br>n Date | Description of Change |

|----------|---------|--------------------|---------------------|-----------------------|

| **       | 3930341 | GVCH               | 03/19/2013          | New Spec              |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### **Products**

Automotive cypress.com/go/automotive Clocks & Buffers cypress.com/go/clocks

Interface cypress.com/go/interface

Lighting & Power Control cypress.com/go/powerpsoc

cypress.com/go/plc

Memory cypress.com/go/memory

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/usb

## PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/go/support

RAMTRON is a registered trademark and NoDelay™ is a trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

© Cypress Semiconductor Corporation, 2011-2013. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.