# Dual 8-/10-/12-/14-/16-Bit 250 MSPS Digital-to-Analog Converters

# AD9741/AD9743/AD9745/AD9746/AD9747

#### **FEATURES**

High dynamic range, dual DACs

Low noise and intermodulation distortion

Single carrier WCDMA ACLR = 80 dBc @ 61.44 MHz IF

Innovative switching output stage permits useable outputs

beyond Nyquist frequency

LVCMOS inputs with dual-port or optional interleaved single-port operation

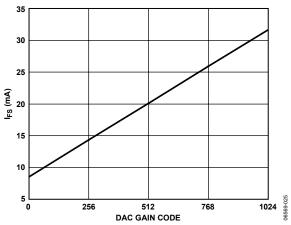

Differential analog current outputs are programmable from 8.6 mA to 31.7 mA full scale

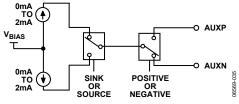

Auxiliary 10-bit current DACs with source/sink capability for external offset nulling

Internal 1.2 V precision reference voltage source Operates from 1.8 V and 3.3 V supplies 315 mW power dissipation Small footprint, Pb-free, 72-Lead LFCSP

#### **APPLICATIONS**

Wireless infrastructure:

WCDMA, CDMA2000, TD-SCDMA, WiMAX

Wideband communications:

LMDS/MMDS, point-to-point

Instrumentation:

RF signal generators, arbitrary waveform generators

#### **GENERAL DESCRIPTION**

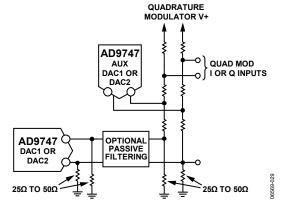

The AD9741/AD9743/AD9745/AD9746/AD9747 are pincompatible, high dynamic range, dual digital-to-analog converters (DACs) with 8-/10-/12-/ 14-/16-bit resolutions and sample rates of up to 250 MSPS. The devices include specific features for direct conversion transmit applications, including gain and offset compensation, and they interface seamlessly with analog quadrature modulators, such as the ADL5370.

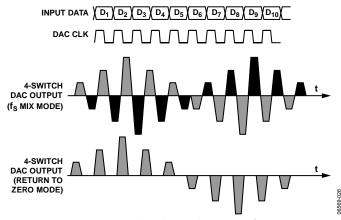

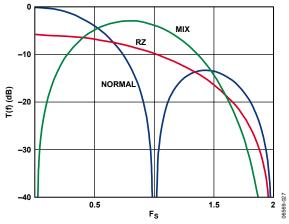

A proprietary, dynamic output architecture permits synthesis of analog outputs even above Nyquist by shifting energy away from the fundamental and into the image frequency.

Full programmability is provided through a serial peripheral interface (SPI) port. In addition, some pin-programmable features are offered for those applications without a controller.

#### **PRODUCT HIGHLIGHTS**

- 1. Low noise and intermodulation distortion (IMD) enables high quality synthesis of wideband signals.

- 2. Proprietary switching output for enhanced dynamic performance.

- 3. Programmable current outputs and dual auxiliary DACs provide flexibility and system enhancements.

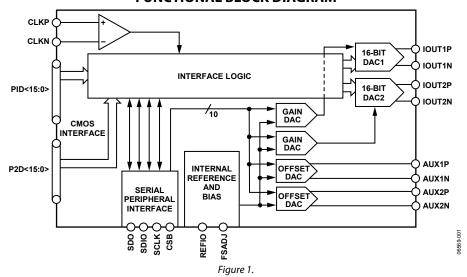

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Product Highlights                           | 1  |

| Functional Block Diagram                     | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| DC Specifications                            | 3  |

| AC Specifications                            | 5  |

| Digital and Timing Specifications            | 7  |

| Absolute Maximum Ratings                     | 8  |

| Thermal Resistance                           | 8  |

| ESD Caution                                  | 8  |

| Pin Configurations and Function Descriptions | 9  |

| Typical Performance Characteristics          | 14 |

| Terminology                                  | 17 |

| Theory of Operation                          | 18 |

| Serial Peripheral Interface                  | 18 |

| General Operation of the Serial Interface    | 18 |

| Instruction Byte                       | . 10 |

|----------------------------------------|------|

| MSB/LSB Transfers                      | . 19 |

| Serial Interface Port Pin Descriptions | . 19 |

| SPI Register Map                       | . 20 |

| SPI Register Descriptions              | . 21 |

| Digital Inputs and Outputs             | . 22 |

| Input Data Timing                      | . 22 |

| Dual-Port Mode Timing                  | . 22 |

| Single-Port Mode Timing                | . 22 |

| SPI Port, Reset, and Pin Mode          | . 22 |

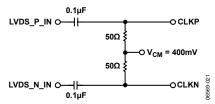

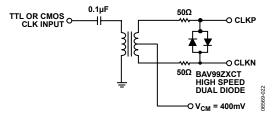

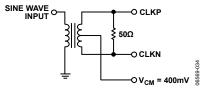

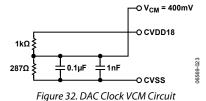

| Driving the DAC Clock Input            | . 23 |

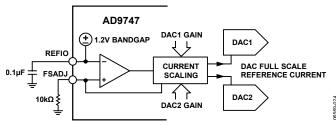

| Full-Scale Current Generation          | . 23 |

| DAC Transfer Function                  | . 24 |

| Analog Modes of Operation              | . 24 |

| Auxiliary DACS                         | . 25 |

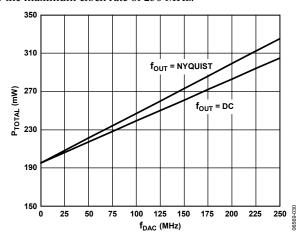

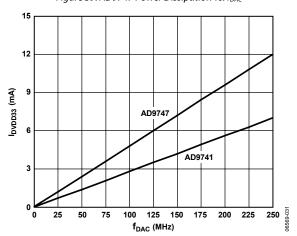

| Power Dissipation                      | . 25 |

| Outline Dimensions                     | . 27 |

| Ordering Guide                         | 27   |

#### **REVISION HISTORY**

5/07—Revision 0: Initial Version

### **SPECIFICATIONS**

### **DC SPECIFICATIONS**

$T_{MIN}$  to  $T_{MAX}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{FS} = 20$  mA, full-scale digital input, maximum sample rate, unless otherwise noted.

Table 1. AD9741, AD9743, and AD9745

|                                                        |      | AD9741 |      |      | AD9743 |      |      | AD9745 |      |        |

|--------------------------------------------------------|------|--------|------|------|--------|------|------|--------|------|--------|

| Parameter                                              | Min  | Тур    | Max  | Min  | Тур    | Max  | Min  | Тур    | Max  | Unit   |

| RESOLUTION                                             |      | 8      |      |      | 10     |      |      | 12     |      | Bits   |

| ACCURACY                                               |      |        |      |      |        |      |      |        |      |        |

| Differential Nonlinearity (DNL)                        |      | ±0.03  |      |      | ±0.05  |      |      | ±0.13  |      | LSB    |

| Integral Nonlinearity (INL)                            |      | ±0.05  |      |      | ±0.10  |      |      | ±0.25  |      | LSB    |

| MAIN DAC OUTPUTS                                       |      |        |      |      |        |      |      |        |      |        |

| Offset Error                                           |      | ±0.001 |      |      | ±0.001 |      |      | ±0.001 |      | %FSR   |

| Offset Error Temperature Coefficient                   |      | 1.0    |      |      | 1.0    |      |      | 1.0    |      | ppm/°C |

| Gain Error                                             |      | ±2.0   |      |      | ±2.0   |      |      | ±2.0   |      | %FSR   |

| Gain Error Temperature Coefficient                     |      | 100    |      |      | 100    |      |      | 100    |      | ppm/°C |

| Gain Matching (DAC1 to DAC2)                           |      | ±1.0   |      |      | ±1.0   |      |      | ±1.0   |      | %FSR   |

| Full-Scale Output Current                              | 8.6  |        | 31.7 | 8.6  |        | 31.7 | 8.6  |        | 31.7 | mA     |

| Output Compliance Voltage                              | -1.0 |        | +1.0 | -1.0 |        | +1.0 | -1.0 |        | +1.0 | V      |

| Output Resistance                                      |      | 10     |      |      | 10     |      |      | 10     |      | ΜΩ     |

| AUXILIARY DAC OUTPUTS                                  |      |        |      |      |        |      |      |        |      |        |

| Resolution                                             |      | 10     |      |      | 10     |      |      | 10     |      | Bits   |

| Full-Scale Output Current                              | -2.0 |        | +2.0 | -2.0 |        | +2.0 | -2.0 |        | +2.0 | mA     |

| Output Compliance Voltage Range—Sink Current           | 0.8  |        | 1.6  | 0.8  |        | 1.6  | 0.8  |        | 1.6  | V      |

| Output Compliance Voltage Range—Source Current         | 0    |        | 1.6  | 0    |        | 1.6  | 0    |        | 1.6  | V      |

| Output Resistance                                      |      | 1      |      |      | 1      |      |      | 1      |      | ΜΩ     |

| Monotonicity                                           | 10   |        |      | 10   |        |      | 10   |        |      | Bits   |

| REFERENCE INPUT/OUTPUT                                 |      |        |      |      |        |      |      |        |      |        |

| Output Voltage                                         |      | 1.2    |      |      | 1.2    |      |      | 1.2    |      | V      |

| Output Voltage Temperature Coefficient                 |      | 10     |      |      | 10     |      |      | 10     |      | ppm/°C |

| External Input Voltage Range                           | 1.15 |        | 1.3  | 1.15 |        | 1.3  | 1.15 |        | 1.3  | V      |

| Input or Output Resistance                             |      | 5      |      |      | 5      |      |      | 5      |      | kΩ     |

| POWER SUPPLY VOLTAGES                                  |      |        |      |      |        |      |      |        |      |        |

| AVDD33, DVDD33                                         | 3.13 |        | 3.47 | 3.13 |        | 3.47 | 3.13 |        | 3.47 | V      |

| CVDD18, DVDD18                                         | 1.70 |        | 1.90 | 1.70 |        | 1.90 | 1.70 |        | 1.90 | V      |

| POWER SUPPLY CURRENTS                                  |      |        |      |      |        |      |      |        |      |        |

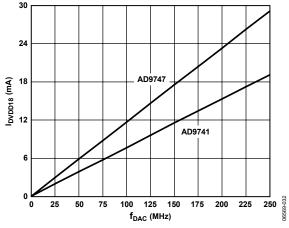

| I <sub>AVDD33</sub>                                    |      | 56     | 60   |      | 56     | 60   |      | 56     | 60   | mA     |

| I <sub>DVDD33</sub>                                    |      | 10     | 14   |      | 10     | 14   |      | 11     | 15   | mA     |

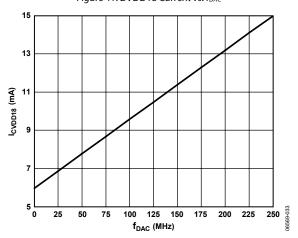

| I <sub>CVDD18</sub>                                    |      | 18     | 22   |      | 18     | 22   |      | 18     | 22   | mA     |

| l <sub>DVDD18</sub>                                    |      | 28     | 32   |      | 29     | 33   |      | 30     | 34   | mA     |

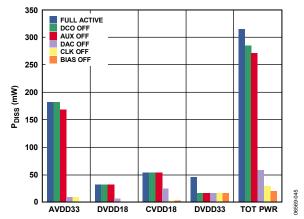

| POWER DISSIPATION                                      |      |        |      |      |        |      |      |        |      |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$ |      | 300    | 345  |      | 300    | 345  |      | 305    | 350  | mW     |

| DAC Outputs Disabled                                   |      | 115    |      |      | 115    |      |      | 120    |      | mW     |

| Full Device Power-Down                                 |      | 3      |      |      | 3      |      |      | 3      |      | mW     |

| OPERATING TEMPERATURE                                  | -40  |        | +85  | -40  |        | +85  | -40  |        | +85  | °C     |

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{FS}}$  = 20 mA, full-scale digital input, maximum sample rate, unless otherwise noted. The AD9745 is repeated in Table 2 so the user can compare it with all other parts.

Table 2. AD9745, AD9746, and AD9747

| AD97                                                   |      | AD9745 |      | AD9746 |        |      |      | AD9747 |      |        |

|--------------------------------------------------------|------|--------|------|--------|--------|------|------|--------|------|--------|

| Parameter                                              | Min  | Тур    | Max  | Min    | Тур    | Max  | Min  | Тур    | Max  | Unit   |

| RESOLUTION                                             |      | 12     |      |        | 14     |      |      | 16     |      | Bits   |

| ACCURACY                                               |      |        |      |        |        |      |      |        |      |        |

| Differential Nonlinearity (DNL)                        |      | ±0.13  |      |        | ±0.5   |      |      | ±2.0   |      | LSB    |

| Integral Nonlinearity (INL)                            |      | ±0.25  |      |        | ±1.0   |      |      | ±4.0   |      | LSB    |

| MAIN DAC OUTPUTS                                       |      |        |      |        |        |      |      |        |      |        |

| Offset Error                                           |      | ±0.001 |      |        | ±0.001 |      |      | ±0.001 |      | %FSR   |

| Offset Error Temperature Coefficient                   |      | 0.1    |      |        | 0.1    |      |      | 0.1    |      | ppm/°C |

| Gain Error                                             |      | ±2.0   |      |        | ±2.0   |      |      | ±2.0   |      | %FSR   |

| Gain Error Temperature Coefficient                     |      | 100    |      |        | 100    |      |      | 100    |      | ppm/°C |

| Gain Matching (DAC1 to DAC2)                           |      | ±1.0   |      |        | ±1.0   |      |      | ±1.0   |      | %FSR   |

| Full-Scale Output Current                              | 8.6  |        | 31.7 | 8.6    |        | 31.7 | 8.6  |        | 31.7 | mA     |

| Output Compliance Voltage                              | -1.0 |        | +1.0 | -1.0   |        | +1.0 | -1.0 |        | +1.0 | ٧      |

| Output Resistance                                      |      | 10     |      |        | 10     |      |      | 10     |      | ΜΩ     |

| AUXILIARY DAC OUTPUTS                                  |      |        |      |        |        |      |      |        |      |        |

| Resolution                                             |      | 10     |      |        | 10     |      |      | 10     |      | Bits   |

| Full-Scale Output Current                              | -2.0 |        | +2.0 | -2.0   |        | +2.0 | -2.0 |        | +2.0 | mA     |

| Output Compliance Voltage Range—Sink Current           | 0.8  |        | 1.6  | 0.8    |        | 1.6  | 0.8  |        | 1.6  | ٧      |

| Output Compliance Voltage Range—Source Current         | 0    |        | 1.6  | 0      |        | 1.6  | 0    |        | 1.6  | ٧      |

| Output Resistance                                      |      | 1      |      |        | 1      |      |      | 1      |      | ΜΩ     |

| Monotonicity                                           | 10   |        |      | 10     |        |      | 10   |        |      | Bits   |

| REFERENCE INPUT/OUTPUT                                 |      |        |      |        |        |      |      |        |      |        |

| Output Voltage                                         |      | 1.2    |      |        | 1.2    |      |      | 1.2    |      | ٧      |

| Output Voltage Temperature Coefficient                 |      | 10     |      |        | 10     |      |      | 10     |      | ppm/°C |

| External Input Voltage Range                           | 1.15 |        | 1.3  | 1.15   |        | 1.3  | 1.15 |        | 1.3  | ٧      |

| Input or Output Resistance                             |      | 5      |      |        | 5      |      |      | 5      |      | kΩ     |

| POWER SUPPLY VOLTAGES                                  |      |        |      |        |        |      |      |        |      |        |

| AVDD33, DVDD33                                         | 3.13 |        | 3.47 | 3.13   |        | 3.47 | 3.13 |        | 3.47 | ٧      |

| CVDD18, DVDD18                                         | 1.70 |        | 1.90 | 1.70   |        | 1.90 | 1.70 |        | 1.90 | V      |

| POWER SUPPLY CURRENTS                                  |      |        |      |        |        |      |      |        |      |        |

| I <sub>AVDD33</sub>                                    |      | 56     | 60   |        | 56     | 60   |      | 56     | 60   | mA     |

| I <sub>DVDD33</sub>                                    |      | 11     | 15   |        | 12     | 16   |      | 12     | 16   | mA     |

| I <sub>CVDD18</sub>                                    |      | 18     | 22   |        | 18     | 22   |      | 18     | 22   | mA     |

| I <sub>DVDD18</sub>                                    |      | 30     | 34   |        | 31     | 35   |      | 32     | 36   | mA     |

| POWER DISSIPATION                                      |      |        |      |        |        |      |      |        |      |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$ |      | 305    | 350  |        | 310    | 355  |      | 310    | 355  | mW     |

| DAC Outputs Disabled                                   |      | 120    |      |        | 125    |      |      | 125    |      | mW     |

| Full Device Power-Down                                 |      | 3      |      |        | 3      |      |      | 3      |      | mW     |

| OPERATING TEMPERATURE                                  | -40  |        | +85  | -40    |        | +85  | -40  |        | +85  | °C     |

#### **AC SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{FS}}$  = 20 mA, full-scale digital input, maximum sample rate, unless otherwise noted.

Table 3. AD9741, AD9743, and AD9745

|                                                                 | AD9741                                 |      |      |      | AD9743 |      |     | AD9745 |        |        |

|-----------------------------------------------------------------|----------------------------------------|------|------|------|--------|------|-----|--------|--------|--------|

| Parameter                                                       | Min                                    | Тур  | Max  | Min  | Тур    | Max  | Min | Тур    | Max    | Unit   |

| SPURIOUS FREE DYNAMIC RANGE (SFDR)                              |                                        |      |      |      |        |      |     |        |        |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$          |                                        | 70   |      |      | 80     |      |     | 82     |        | dBc    |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |                                        | 70   |      |      | 70     |      |     | 70     |        | dBc    |

| $f_{DAC} = 250 \text{ MSPS}$ , $f_{OUT} = 180 \text{ MHz}^1$    |                                        | 64   |      |      | 64     |      |     | 66     |        | dBc    |

| INTERMODULATION DISTORTION (IMD)                                |                                        |      |      |      |        |      |     |        |        |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$          |                                        | 80   |      |      | 80     |      |     | 86     |        | dBc    |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |                                        | 80   |      |      | 80     |      |     | 80     |        | dBc    |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 180 \text{ MHz}^1$       |                                        | 72   |      |      | 72     |      |     | 74     |        | dBc    |

| CROSSTALK                                                       |                                        |      |      |      |        |      |     |        |        |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$          |                                        | 80   |      |      | 80     |      |     | 80     |        | dBc    |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |                                        | 80   |      | 80   |        |      | 80  |        | dBc    |        |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 180 \text{ MHz}^1$       |                                        | 80   |      |      | 80     |      |     | 80     |        | dBc    |

| ADJACENT CHANNEL LEAKAGE RATIO (ACLR) SINGLE CARRIER WCDMA      |                                        |      |      |      |        |      |     |        |        |        |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 15.36 \text{ MHz}$    |                                        | 54   |      |      | 66     |      |     | 76     |        | dBc    |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 61.44 \text{ MHz}$    |                                        | 54   |      |      | 66     |      |     | 76     |        | dBc    |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 184.32 \text{ MHz}^1$ | $S, f_{OUT} = 184.32 \text{ MHz}^1$ 54 |      |      | 64   |        |      | 72  |        | dBc    |        |

| NOISE SPECTRAL DENSITY (NSD)                                    |                                        |      |      |      |        |      |     |        |        |        |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 15.36 \text{ MHz}$    | -132                                   |      | -132 |      | -144   |      |     | dBm/Hz |        |        |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 61.44 \text{ MHz}$    |                                        | -132 |      | -132 |        | -144 |     |        | dBm/Hz |        |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 184.32 \text{ MHz}^1$ |                                        | -135 |      |      | -147   |      |     | -155   |        | dBm/Hz |

<sup>&</sup>lt;sup>1</sup> Mix Mode.

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{FS}}$  = 20 mA, full-scale digital input, maximum sample rate, unless otherwise noted. The AD9745 is repeated in Table 4 so the user can compare it with all other parts.

Table 4. AD9745, AD9746, and AD9747

|                                                                 |      | AD9745 |           |      | AD9746 |           |      | AD974 |        |      |

|-----------------------------------------------------------------|------|--------|-----------|------|--------|-----------|------|-------|--------|------|

| Parameter                                                       | Min  | Тур    | Max       | Min  | Тур    | Max       | Min  | Тур   | Max    | Unit |

| SPURIOUS FREE DYNAMIC RANGE (SFDR)                              |      |        |           |      |        |           |      |       |        |      |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$          |      | 82     |           |      | 82     |           |      | 82    |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |      | 70     |           |      | 70     |           |      | 70    |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 180 \text{ MHz}^1$       |      | 66     |           |      | 66     |           |      | 66    |        | dBc  |

| INTERMODULATION DISTORTION (IMD)                                |      |        |           |      |        |           |      |       |        |      |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 20 \text{ MHz}$          |      | 86     |           |      | 86     |           |      | 86    |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |      | 80     |           |      | 80     |           |      | 80    |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 180 \text{ MHz}^1$       |      | 74     |           |      | 74     |           |      | 74    |        | dBc  |

| CROSSTALK                                                       |      |        |           |      |        |           |      |       |        |      |

| $f_{DAC} = 250$ MSPS, $f_{OUT} = 20$ MHz                        |      | 80     |           |      | 80     |           |      | 80    |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 70 \text{ MHz}$          |      | 80     |           | 80   |        |           | 80   |       |        | dBc  |

| $f_{DAC} = 250 \text{ MSPS}, f_{OUT} = 180 \text{ MHz}^1$       |      | 80     |           | 80   |        | 80        |      |       | dBc    |      |

| ADJACENT CHANNEL LEAKAGE RATIO (ACLR) SINGLE CARRIER WCDMA      |      |        |           |      |        |           |      |       |        |      |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 15.36 \text{ MHz}$    |      | 76     |           |      | 78     |           |      | 82    |        | dBc  |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 61.44 \text{ MHz}$    |      | 76     |           |      | 78     |           |      | 80    |        | dBc  |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 184.32 \text{ MHz}^1$ | 72   |        |           |      | 74     |           |      | 74    |        | dBc  |

| NOISE SPECTRAL DENSITY (NSD)                                    |      |        |           |      |        |           |      |       |        |      |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 15.36 \text{ MHz}$    | -155 |        | -155 -163 |      | -163   | -163 -165 |      |       | dBm/Hz |      |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 61.44 \text{ MHz}$    |      | -155   |           | -155 |        | -160      |      |       | dBm/Hz |      |

| $f_{DAC} = 245.76 \text{ MSPS}, f_{OUT} = 184.32 \text{ MHz}^1$ |      | -155   |           | -158 |        |           | -160 |       | dBm/Hz |      |

<sup>&</sup>lt;sup>1</sup> Mix Mode.

#### **DIGITAL AND TIMING SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{FS}}$  = 20 mA, full-scale digital input, maximum sample rate, unless otherwise noted.

Table 5. AD9741/AD9743/AD9745/AD9746/AD9747

| Parameter                                                           | Min  | Тур  | Max  | Unit   |

|---------------------------------------------------------------------|------|------|------|--------|

| DAC CLOCK INPUTS (CLKP, CLKN)                                       |      |      |      |        |

| Differential Peak-to-Peak Voltage                                   | 400  | 800  | 1600 | mV     |

| Single-Ended Peak-to-Peak Voltage                                   |      |      | 800  | mV     |

| Common-Mode Voltage                                                 | 300  | 400  | 500  | mV     |

| Input Current                                                       |      |      | 1    | μΑ     |

| Input Frequency                                                     |      |      | 250  | MHz    |

| DATA CLOCK OUTPUT (DCO)                                             |      |      |      |        |

| Output Voltage High                                                 | 2.4  |      |      | V      |

| Output Voltage Low                                                  |      |      | 0.4  | V      |

| Output Current                                                      |      |      | 10   | mA     |

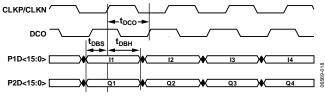

| DAC Clock to Data Clock Output Delay (t <sub>DCO</sub> )            | 2.0  | 2.2  | 2.8  | ns     |

| DATA PORT INPUTS                                                    |      |      |      |        |

| Input Voltage High                                                  | 2.0  |      |      | V      |

| Input Voltage Low                                                   |      |      | 8.0  | V      |

| Input Current                                                       |      |      | 1    | μΑ     |

| Data to DAC Clock Setup Time (tdbs Dual-Port Mode)                  | 400  |      |      | ps     |

| Data to DAC Clock Hold Time (tdbh Dual-Port Mode)                   | 1200 |      |      | ps     |

| DAC Clock to Analog Output Data Latency (Dual-Port Mode)            |      |      | 7    | Cycles |

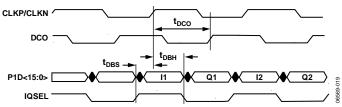

| Data or IQSEL Input to DAC Clock Setup Time (tdbs Single-Port Mode) | 400  |      |      | ps     |

| Data or IQSEL Input to DAC Clock Hold Time (tdbH Single-Port Mode)  | 1200 |      |      | ps     |

| DAC Clock to Analog Output Data Latency (Single-Port Mode)          |      |      | 8    | Cycles |

| SERIAL PERIPHERAL INTERFACE                                         |      |      |      |        |

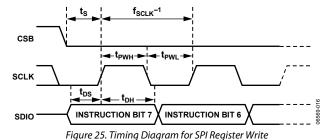

| SCLK Frequency (f <sub>SCLK</sub> )                                 |      |      | 40   | MHz    |

| SCLK Pulse Width High (t <sub>PWH</sub> )                           | 10   |      |      | ns     |

| SCLK Pulse Width Low (t <sub>PWL</sub> )                            | 10   |      |      | ns     |

| CSB to SCLK Setup Time (ts)                                         | 1    |      |      | ns     |

| CSB to SCLK Hold Time (t <sub>H</sub> )                             | 0    |      |      | ns     |

| SDIO to SCLK Setup Time (t <sub>DS</sub> )                          | 1    |      |      | ns     |

| SDIO to SCLK Hold Time (t <sub>DH</sub> )                           | 0    |      |      | ns     |

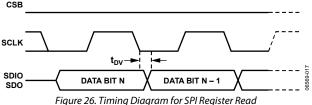

| SCLK to SDIO/SDO Data Valid Time (t <sub>DV</sub> )                 |      |      | 1    | ns     |

| RESET Pulse Width High                                              | 10   |      |      | ns     |

| WAKE-UP TIME AND OUTPUT LATENCY                                     |      |      |      |        |

| From DAC Outputs Disabled                                           |      | 200  |      | μs     |

| From Full Device Power-Down                                         |      | 1200 |      | μs     |

| DAC Clock to Analog Output Latency (Dual-Port Mode)                 |      | 7    |      | Cycles |

| DAC Clock to Analog Output Latency (Single-Port Mode)               |      | 8    |      | Cycles |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

|                             | With       |                          |

|-----------------------------|------------|--------------------------|

| Parameter                   | Respect to | Rating                   |

| AVDD33, DVDD33              | AVSS DVSS  | −0.3 V to +3.6 V         |

|                             | CVSS       |                          |

| DVDD18, CVDD18              | AVSS DVSS  | -0.3 V to +1.98 V        |

|                             | CVSS       |                          |

| AVSS                        | DVSS CVSS  | −0.3 V to +0.3 V         |

| DVSS                        | AVSS CVSS  | -0.3 V to +0.3 V         |

| CVSS                        | AVSS DVSS  | −0.3 V to +0.3 V         |

| REFIO                       | AVSS       | -0.3 V to AVDD33 + 0.3 V |

| IOUT1P, IOUT1N, IOUT2P,     | AVSS       | -1.0 V to AVDD33 + 0.3 V |

| IOUT2P, AUX1P, AUX1N,       |            |                          |

| AUX2P, AUX2N                |            |                          |

| P1D15 to P1D0,              | DVSS       | -0.3 V to DVDD33 + 0.3 V |

| P2D15 to P2D0               |            |                          |

| CLKP, CLKN                  | CVSS       | -0.3 V to CVDD18 + 0.3 V |

| RESET, CSB, SCLK, SDIO, SDO | DVSS       | -0.3 V to DVDD33 + 0.3 V |

| Junction Temperature        |            | 125°C                    |

| Storage Temperature         |            | −65°C to +150°C          |

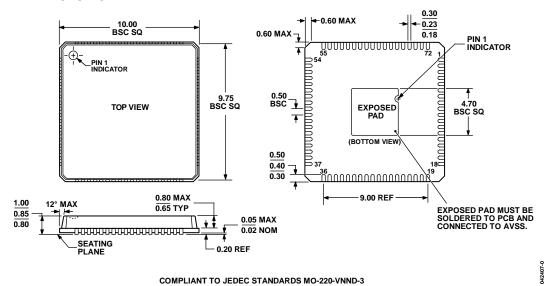

#### THERMAL RESISTANCE

Thermal resistance tested using JEDEC standard 4-layer thermal test board with no airflow.

Table 7.

| Package Type                          | $\boldsymbol{\theta}_{JA}$ | Unit |

|---------------------------------------|----------------------------|------|

| CP-72-1 (Exposed Pad Soldered to PCB) | 25                         | °C/W |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

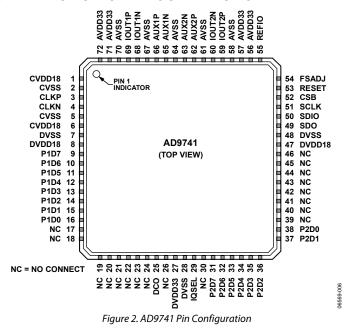

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

**Table 8. AD 9741 Pin Function Descriptions**

| Pin No.                    | Mnemonic | Description                                                                                                                                                                             |

|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6                       | CVDD18   | Clock Supply Voltage (1.8 V).                                                                                                                                                           |

| 2, 5                       | CVSS     | Clock Supply Common (0 V).                                                                                                                                                              |

| 3                          | CLKP     | Differential DAC Clock Input.                                                                                                                                                           |

| 4                          | CLKN     | Complementary Differential DAC Clock Input.                                                                                                                                             |

| 7, 28, 48                  | DVSS     | Digital Supply Common (0 V).                                                                                                                                                            |

| 8, 47                      | DVDD18   | Digital Core Supply Voltage (1.8 V).                                                                                                                                                    |

| 9 to 16                    | P1D<7:0> | Port 1 Data Bit Inputs.                                                                                                                                                                 |

| 17 to 24, 26, 30, 39 to 46 | NC       | No Connect.                                                                                                                                                                             |

| 25                         | DCO      | Data Clock Output. Use to clock data source.                                                                                                                                            |

| 27                         | DVDD33   | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                     |

| 29                         | IQSEL    | I/Q Framing Signal for Single-Port Mode Operation.                                                                                                                                      |

| 31 to 38                   | P2D<7:0> | Port 2 Data Bit Inputs.                                                                                                                                                                 |

| 49                         | SDO      | Serial Peripheral Interface Data Output.                                                                                                                                                |

| 50                         | SDIO     | Serial Peripheral Interface Data Input and Optional Data Output.                                                                                                                        |

| 51                         | SCLK     | Serial Peripheral Interface Clock Input.                                                                                                                                                |

| 52                         | CSB      | Serial Peripheral Interface Chip Select Input. Active low.                                                                                                                              |

| 53                         | RESET    | Hardware Reset. Active high.                                                                                                                                                            |

| 54                         | FSADJ    | Full-Scale Current Output Adjust. Connect a 10 kΩ resistor to AVSS.                                                                                                                     |

| 55                         | REFIO    | Reference Input/Output. Connect a 0.1 μF capacitor to AVSS.                                                                                                                             |

| 56, 57, 71, 72             | AVDD33   | Analog Supply Voltage (3.3 V).                                                                                                                                                          |

| 58, 61, 64, 67, 70         | AVSS     | Analog Supply Common (0 V).                                                                                                                                                             |

| 59                         | IOUT2P   | DAC2 Current Output True. Sources full-scale current when input data bits are all 1.                                                                                                    |

| 60                         | IOUT2N   | DAC2 Current Output Complement. Sources full-scale current when data bits are all 0.                                                                                                    |

| 62                         | AUX2P    | Auxiliary DAC2 Default Current Output Pin.                                                                                                                                              |

| 63                         | AUX2N    | Auxiliary DAC2 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 65                         | AUX1N    | Auxiliary DAC1 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 66                         | AUX1P    | Auxiliary DAC1 Default Current Output Pin.                                                                                                                                              |

| 68                         | IOUT1N   | Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.                                                                                                 |

| 69                         | IOUT1P   | DAC1 Current Output. Sources full-scale current when data bits are all 1.                                                                                                               |

| EPAD                       | AVSS     | Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical stability and must be electrically tied to low impedance GND plane for low noise performance. |

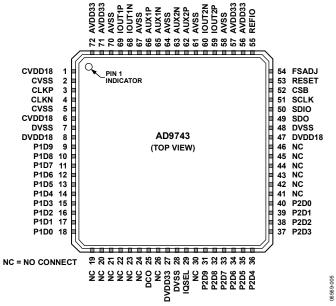

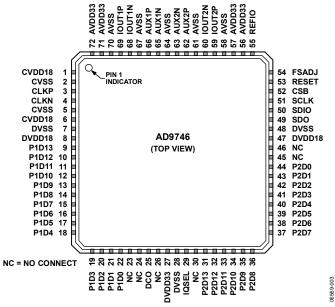

Figure 3. AD9743 Pin Configuration

**Table 9. AD 9743 Pin Function Descriptions**

| Pin No.                    | Mnemonic | Description                                                                                                                                                                             |

|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6                       | CVDD18   | Clock Supply Voltage (1.8 V).                                                                                                                                                           |

| 2, 5                       | CVSS     | Clock Supply Common (0 V).                                                                                                                                                              |

| 3                          | CLKP     | Differential DAC Clock Input.                                                                                                                                                           |

| 4                          | CLKN     | Complementary Differential DAC Clock Input.                                                                                                                                             |

| 7, 28, 48                  | DVSS     | Digital Supply Common (0 V).                                                                                                                                                            |

| 8, 47                      | DVDD18   | Digital Core Supply Voltage (1.8 V).                                                                                                                                                    |

| 9 to 18                    | P1D<9:0> | Port 1 Data Bit Inputs.                                                                                                                                                                 |

| 19 to 24, 26, 30, 41 to 46 | NC       | No Connect.                                                                                                                                                                             |

| 25                         | DCO      | Data Clock Output. Use to clock data source.                                                                                                                                            |

| 27                         | DVDD33   | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                     |

| 29                         | IQSEL    | I/Q Framing Signal for Single-Port Mode Operation.                                                                                                                                      |

| 31 to 40                   | P2D<9:0> | Port 2 Data Bit Inputs.                                                                                                                                                                 |

| 49                         | SDO      | Serial Peripheral Interface Data Output.                                                                                                                                                |

| 50                         | SDIO     | Serial Peripheral Interface Data Input and Optional Data Output.                                                                                                                        |

| 51                         | SCLK     | Serial Peripheral Interface Clock Input.                                                                                                                                                |

| 52                         | CSB      | Serial Peripheral Interface Chip Select Input. Active low.                                                                                                                              |

| 53                         | RESET    | Hardware Reset. Active high.                                                                                                                                                            |

| 54                         | FSADJ    | Full-Scale Current Output Adjust. Connect a 10 kΩ resistor to AVSS.                                                                                                                     |

| 55                         | REFIO    | Reference Input/Output. Connect a 0.1 μF capacitor to AVSS.                                                                                                                             |

| 56, 57, 71, 72             | AVDD33   | Analog Supply Voltage (3.3 V).                                                                                                                                                          |

| 58, 61, 64, 67, 70         | AVSS     | Analog Supply Common (0 V).                                                                                                                                                             |

| 59                         | IOUT2P   | DAC2 Current Output True. Sources full-scale current when input data bits are all 1.                                                                                                    |

| 60                         | IOUT2N   | DAC2 Current Output Complement. Sources full-scale current when data bits are all 0.                                                                                                    |

| 62                         | AUX2P    | Auxiliary DAC2 Default Current Output Pin.                                                                                                                                              |

| 63                         | AUX2N    | Auxiliary DAC2 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 65                         | AUX1N    | Auxiliary DAC1 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 66                         | AUX1P    | Auxiliary DAC1 Default Current Output Pin.                                                                                                                                              |

| 68                         | IOUT1N   | Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.                                                                                                 |

| 69                         | IOUT1P   | DAC1 Current Output. Sources full-scale current when data bits are all 1.                                                                                                               |

| EPAD                       | AVSS     | Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical stability and must be electrically tied to low impedance GND plane for low noise performance. |

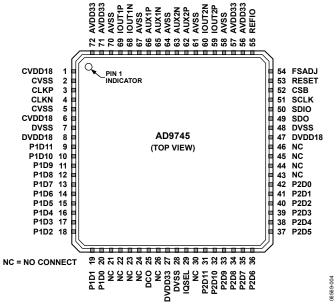

Figure 4. AD9745 Pin Configuration

Table 10. AD9745 Pin Function Descriptions

| Pin No.                    | Mnemonic  | Description                                                                                                                                                                             |

|----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6                       | CVDD18    | Clock Supply Voltage (1.8 V).                                                                                                                                                           |

| 2, 5                       | CVSS      | Clock Supply Common (0 V).                                                                                                                                                              |

| 3                          | CLKP      | Differential DAC Clock Input.                                                                                                                                                           |

| 4                          | CLKN      | Complementary Differential DAC Clock Input.                                                                                                                                             |

| 7, 28, 48                  | DVSS      | Digital Supply Common (0 V).                                                                                                                                                            |

| 8, 47                      | DVDD18    | Digital Core Supply Voltage (1.8 V).                                                                                                                                                    |

| 9 to 20                    | P1D<11:0> | Port 1 Data Bit Inputs.                                                                                                                                                                 |

| 21 to 24, 26, 30, 43 to 46 | NC        | No Connect.                                                                                                                                                                             |

| 25                         | DCO       | Data Clock Output. Use to clock data source.                                                                                                                                            |

| 27                         | DVDD33    | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                     |

| 29                         | IQSEL     | I/Q Framing Signal for Single-Port Mode Operation.                                                                                                                                      |

| 31 to 42                   | P2D<11:0> | Port 2 Data Bit Inputs.                                                                                                                                                                 |

| 49                         | SDO       | Serial Peripheral Interface Data Output.                                                                                                                                                |

| 50                         | SDIO      | Serial Peripheral Interface Data Input and Optional Data Output.                                                                                                                        |

| 51                         | SCLK      | Serial Peripheral Interface Clock Input.                                                                                                                                                |

| 52                         | CSB       | Serial Peripheral Interface Chip Select Input. Active low.                                                                                                                              |

| 53                         | RESET     | Hardware Reset. Active high.                                                                                                                                                            |

| 54                         | FSADJ     | Full-Scale Current Output Adjust. Connect 10 kΩ resistor to AVSS.                                                                                                                       |

| 55                         | REFIO     | Reference Input/Output. Connect a 0.1 µF capacitor to AVSS.                                                                                                                             |

| 56, 57, 71, 72             | AVDD33    | Analog Supply Voltage (3.3 V).                                                                                                                                                          |

| 58, 61, 64, 67, 70         | AVSS      | Analog Supply Common (0 V).                                                                                                                                                             |

| 59                         | IOUT2P    | DAC2 Current Output True. Sources full-scale current when input data bits are all 1.                                                                                                    |

| 60                         | IOUT2N    | DAC2 Current Output Complement. Sources full-scale current when data bits are all 0.                                                                                                    |

| 62                         | AUX2P     | Auxiliary DAC2 Default Current Output Pin.                                                                                                                                              |

| 63                         | AUX2N     | Auxiliary DAC2 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 65                         | AUX1N     | Auxiliary DAC1 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 66                         | AUX1P     | Auxiliary DAC1 Default Current Output Pin.                                                                                                                                              |

| 68                         | IOUT1N    | Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.                                                                                                 |

| 69                         | IOUT1P    | DAC1 Current Output. Sources full-scale current when data bits are all 1.                                                                                                               |

| EPAD                       | AVSS      | Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical stability and must be electrically tied to low impedance GND plane for low noise performance. |

Figure 5. AD9746 Pin Configuration

| Table 11. AD9746 P     | 1         | 1                                                                                                                                                                                      |

|------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                | Mnemonic  | Description                                                                                                                                                                            |

| 1, 6                   | CVDD18    | Clock Supply Voltage (1.8 V).                                                                                                                                                          |

| 2, 5                   | CVSS      | Clock Supply Common (0 V).                                                                                                                                                             |

| 3                      | CLKP      | Differential DAC Clock Input.                                                                                                                                                          |

| 4                      | CLKN      | Complementary Differential DAC Clock Input.                                                                                                                                            |

| 7, 28, 48              | DVSS      | Digital Supply Common (0 V).                                                                                                                                                           |

| 8, 47                  | DVDD18    | Digital Core Supply Voltage (1.8 V).                                                                                                                                                   |

| 9 to 22                | P1D<13:0> | Port 1 Data Bit Inputs.                                                                                                                                                                |

| 23, 24, 26, 30, 45, 46 | NC        | No Connect.                                                                                                                                                                            |

| 25                     | DCO       | Data Clock Output. Use to clock data source.                                                                                                                                           |

| 27                     | DVDD33    | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                    |

| 29                     | IQSEL     | I/Q Framing Signal for Single-Port Mode Operation.                                                                                                                                     |

| 31 to 44               | P2D<13:0> | Port 2 Data Bit Inputs.                                                                                                                                                                |

| 49                     | SDO       | Serial Peripheral Interface Data Output.                                                                                                                                               |

| 50                     | SDIO      | Serial Peripheral Interface Data Input and Optional Data Output.                                                                                                                       |

| 51                     | SCLK      | Serial Peripheral Interface Clock Input.                                                                                                                                               |

| 52                     | CSB       | Serial Peripheral Interface Chip Select Input. Active low.                                                                                                                             |

| 53                     | RESET     | Hardware Reset. Active high.                                                                                                                                                           |

| 54                     | FSADJ     | Full-Scale Current Output Adjust. Connect a 10 kΩ resistor to AVSS.                                                                                                                    |

| 55                     | REFIO     | Reference Input/Output. Connect a 0.1 μF capacitor to AVSS.                                                                                                                            |

| 56, 57, 71, 72         | AVDD33    | Analog Supply Voltage (3.3 V).                                                                                                                                                         |

| 58, 61, 64, 67, 70     | AVSS      | Analog Supply Common (0 V).                                                                                                                                                            |

| 59                     | IOUT2P    | DAC2 Current Output True. Sources full-scale current when input data bits are all 1.                                                                                                   |

| 60                     | IOUT2N    | DAC2 Current Output Complement. Sources full-scale current when data bits are all 0.                                                                                                   |

| 62                     | AUX2P     | Auxiliary DAC2 Default Current Output Pin.                                                                                                                                             |

| 63                     | AUX2N     | Auxiliary DAC2 Optional Output Pin. Enable through SPI.                                                                                                                                |

| 65                     | AUX1N     | Auxiliary DAC1 Optional Output Pin. Enable through SPI.                                                                                                                                |

| 66                     | AUX1P     | Auxiliary DAC1 Default Current Output Pin.                                                                                                                                             |

| 68                     | IOUT1N    | Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.                                                                                                |

| 69                     | IOUT1P    | DAC1 Current Output. Sources full-scale current when data bits are all 1.                                                                                                              |

| EPAD                   | AVSS      | Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical stabilit and must be electrically tied to low impedance GND plane for low noise performance. |

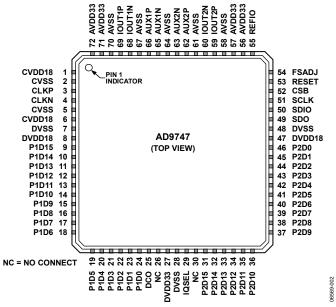

Figure 6. AD9747 Pin Configuration

Table 12. AD9747 Pin Function Descriptions

| Pin No.            | Mnemonic  | Description                                                                                                                                                                             |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6               | CVDD18    | Clock Supply Voltage (1.8 V).                                                                                                                                                           |

| 2, 5               | CVSS      | Clock Supply Common (0 V).                                                                                                                                                              |

| 3                  | CLKP      | Differential DAC Clock Input.                                                                                                                                                           |

| 4                  | CLKN      | Complementary Differential DAC Clock Input.                                                                                                                                             |

| 7, 28, 48          | DVSS      | Digital Supply Common (0 V).                                                                                                                                                            |

| 8, 47              | DVDD18    | Digital Core Supply Voltage (1.8 V).                                                                                                                                                    |

| 9 to 24            | P1D<15:0> | Port 1 Data Bit Inputs.                                                                                                                                                                 |

| 25                 | DCO       | Data Clock Output. Use to clock data source.                                                                                                                                            |

| 26, 30             | NC        | No Connect.                                                                                                                                                                             |

| 27                 | DVDD33    | Digital I/O Supply Voltage (3.3 V).                                                                                                                                                     |

| 29                 | IQSEL     | I/Q Framing Signal for Single-Port Mode Operation.                                                                                                                                      |

| 31 to 46           | P2D<15:0> | Port 2 Data Bit Inputs.                                                                                                                                                                 |

| 49                 | SDO       | Serial Peripheral Interface Data Output.                                                                                                                                                |

| 50                 | SDIO      | Serial Peripheral Interface Data Input and Optional Data Output.                                                                                                                        |

| 51                 | SCLK      | Serial Peripheral Interface Clock Input.                                                                                                                                                |

| 52                 | CSB       | Serial Peripheral Interface Chip Select Input. Active low.                                                                                                                              |

| 53                 | RESET     | Hardware Reset. Active high.                                                                                                                                                            |

| 54                 | FSADJ     | Full-Scale Current Output Adjust. Connect a 10 kΩ resistor to AVSS.                                                                                                                     |

| 55                 | REFIO     | Reference Input/Output. Connect a 0.1 µF capacitor to AVSS.                                                                                                                             |

| 56, 57, 71, 72     | AVDD33    | Analog Supply Voltage (3.3 V).                                                                                                                                                          |

| 58, 61, 64, 67, 70 | AVSS      | Analog Supply Common (0 V).                                                                                                                                                             |

| 59                 | IOUT2P    | DAC2 Current Output. Sources full-scale current when input data bits are all 1.                                                                                                         |

| 60                 | IOUT2N    | Complementary DAC2 Current Output. Sources full-scale current when data bits are all 0.                                                                                                 |

| 62                 | AUX2P     | Auxiliary DAC2 Default Current Output Pin.                                                                                                                                              |

| 63                 | AUX2N     | Auxiliary DAC2 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 65                 | AUX1N     | Auxiliary DAC1 Optional Output Pin. Enable through SPI.                                                                                                                                 |

| 66                 | AUX1P     | Auxiliary DAC1 Default Current Output Pin.                                                                                                                                              |

| 68                 | IOUT1N    | Complementary DAC1 Current Output. Sources full-scale current when data bits are all 0.                                                                                                 |

| 69                 | IOUT1P    | DAC1 Current Output. Sources full-scale current when data bits are all 1.                                                                                                               |

| EPAD               | AVSS      | Exposed Thermal Pad. Must be soldered to copper pour on top surface of PCB for mechanical stability and must be electrically tied to low impedance GND plane for low noise performance. |

### TYPICAL PERFORMANCE CHARACTERISTICS

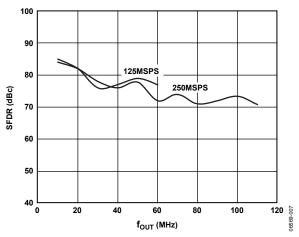

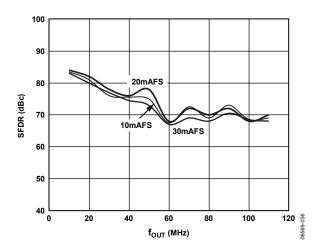

Figure 7. AD9747 SFDR vs. fout, Normal Mode

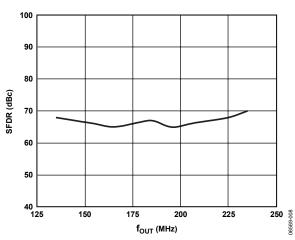

Figure 8. AD9747 SFDR vs. fout, Mix Mode, 250 MSPS

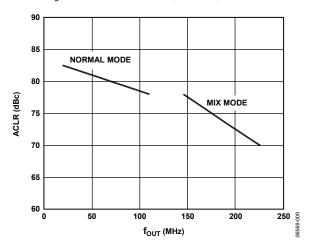

Figure 9. AD9747 ACLR vs. fout, Single Carrier WCDMA, 245.76 MSPS

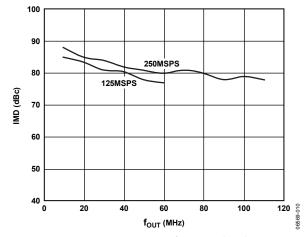

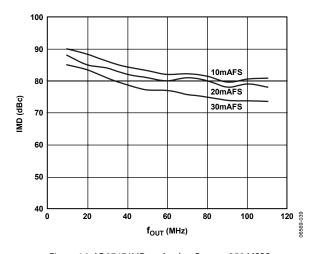

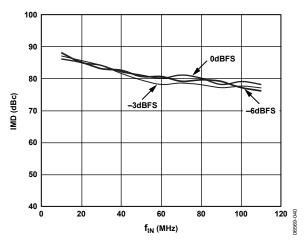

Figure 10. AD9747 IMD vs. fout, Normal Mode

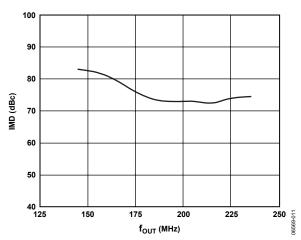

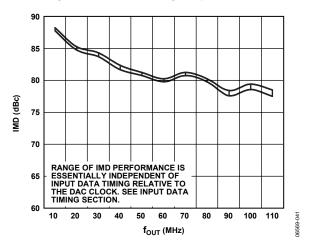

Figure 11. AD9747 IMD vs. f<sub>OUT</sub>, Mix Mode, 250 MSPS

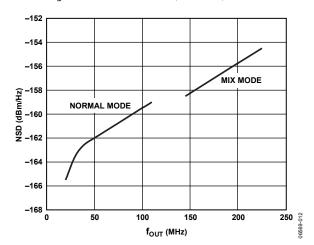

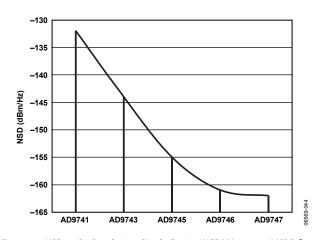

Figure 12. AD9747 NSD vs. f<sub>OUT</sub>, Single Carrier WCDMA, 245.76 MSPS

Figure 13. AD9747 SFDR vs. Analog Output, 250 MSPS

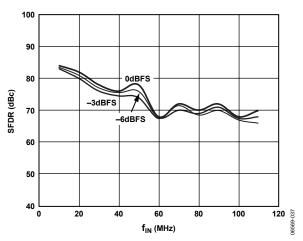

Figure 14. AD9747 SFDR vs. Digital Input, 250 MSPS

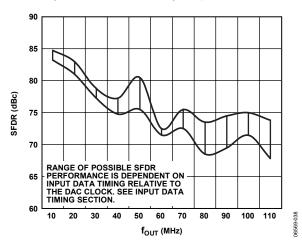

Figure 15. AD9747 SFDR vs. f<sub>OUT</sub> Over Input Data Timing

Figure 16. AD9747 IMD vs. Analog Output, 250 MSPS

Figure 17. AD9747 IMD vs. Digital Input, 250 MSPS

Figure 18. AD9747 IMD vs. fout Over Input Data Timing

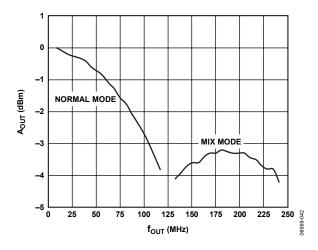

Figure 19. Nominal Power in the Fundamental,  $I_{FS} = 20 \text{ mA}$

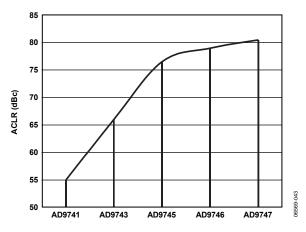

Figure 20. ACLR vs. Bit Resolution, Single Carrier WCDMA, 245.76 MSPS,  $f_{CARRIER} = 61.44 \text{ MHz}$

Figure 21. NSD vs. Bit Resolution, Single Carrier WCDMA, 245.76 MSPS,  $f_{CARRIER} = 61.44$  MHz

### **TERMINOLOGY**

#### **Integral Nonlinearity (INL)**

The maximum deviation of the actual analog output from the ideal output, as determined by a straight line drawn from zero scale to full scale.

#### Differential Nonlinearity (DNL)

A measure of the maximum deviation in analog output associated with any single value change in the digital input code relative to an ideal LSB.

#### Monotonicity

A DAC is monotonic if the analog output increases or remains constant in response to an increase in the digital input.

#### **Offset Error**

The deviation of the output current from the ideal zero-scale current. For differential outputs, 0 mA is expected at  $I_{\text{OUTP}}$  when all inputs are low, and 0 mA is expected at  $I_{\text{OUTN}}$  when all inputs are high.

#### **Gain Error**

The deviation of the output current from the ideal full-scale current. Actual full-scale output current is determined by subtracting the output (when all inputs are low) from the output (when all inputs are high).

#### **Output Compliance Range**

The range of allowable voltage seen by the analog output of a current output DAC. Operation beyond the compliance limits may cause output stage saturation and/or a breakdown resulting in nonlinear performance.

#### **Temperature Drift**

Temperature drift is specified as the maximum change in a parameter from ambient temperature (25°C) to either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$  and is typically reported as ppm/°C.

#### Spurious-Free Dynamic Range (SFDR)

The difference in decibels between the peak amplitude of a test tone and the peak amplitude of the largest spurious signal over the specified bandwidth.

#### **Intermodulation Distortion (IMD)**

The difference in decibels between the maximum peak amplitude of two test tones and the maximum peak amplitude of the distortion products created from the sum or difference of integer multiples of the test tones.

#### Adjacent Channel Leakage Ratio (ACLR)

The ratio between the measured power of a wideband signal within a channel relative to the measured power in an empty adjacent channel.

#### Noise Spectral Density (NSD)

The measured noise power over a 1 Hz bandwidth seen at the analog output.

### THEORY OF OPERATION

The AD9741/AD9743/AD9745/AD9746/AD9747 combine many features to make them very attractive for wired and wireless communications systems. The dual DAC architecture facilitates easy interfacing to common quadrature modulators when designing single sideband transmitters. In addition, the speed and performance of the devices allow wider bandwidths and more carriers to be synthesized than in previously available products.

All features and options are software programmable through the SPI port.

#### **SERIAL PERIPHERAL INTERFACE**

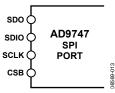

Figure 22. SPI Port

The SPI port is a flexible, synchronous serial communications port allowing easy interfacing to many industry-standard microcontrollers and microprocessors. The port is compatible with most synchronous transfer formats including both the Motorola SPI and Intel® SSR protocols.

The interface allows read and write access to all registers that configure the AD9741/AD9743/AD9745/AD9746/AD9747. Single or multiple byte transfers are supported as well as MSB-first or LSB-first transfer formats. Serial data input/output can be accomplished through a single bidirectional pin (SDIO) or through two unidirectional pins (SDIO/SDO).

The serial port configuration is controlled by Register 0x00, Bits<7:6>. It is important to note that any change made to the serial port configuration occurs immediately upon writing to the last bit of this byte. Therefore, it is possible with a multibyte transfer to write to this register and change the configuration in the middle of a communication cycle. Care must be taken to compensate for the new configuration within the remaining bytes of the current communication cycle.

Use of a single-byte transfer when changing the serial port configuration is recommended to prevent unexpected device behavior.

#### **GENERAL OPERATION OF THE SERIAL INTERFACE**

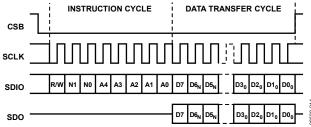

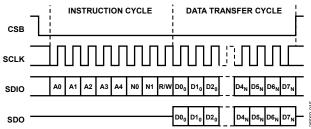

There are two phases to any communication cycle with the AD9741/AD9743/AD9745/AD9746/AD9747: Phase 1 and Phase 2. Phase 1 is the instruction cycle, which writes an instruction byte into the device. This byte provides the serial port controller with information regarding Phase 2 of the communication cycle: the data transfer cycle.

The Phase 1 instruction byte defines whether the upcoming data transfer is read or write, the number of bytes in the data

transfer, and a reference register address for the first byte of the data transfer. A logic high on the CSB pin followed by a logic low resets the SPI port to its initial state and defines the start of the instruction cycle. From this point, the next eight rising SCLK edges define the eight bits of the instruction byte for the current communication cycle.

The remaining SCLK edges are for Phase 2 of the communication cycle, which is the data transfer between the serial port controller and the system controller. Phase 2 can be a transfer of 1, 2, 3, or 4 data bytes as determined by the instruction byte. Using multibyte transfers is usually preferred although single-byte data transfers are useful to reduce CPU overhead or when only a single register access is required.

All serial port data is transferred to and from the device in synchronization with the SCLK pin. Input data is always latched on the rising edge of SCLK whereas output data is always valid after the falling edge of SCLK. Register contents change immediately upon writing to the last bit of each transfer byte.

When synchronization is lost, the device has the ability to asynchronously terminate an I/O operation whenever the CSB pin is taken to logic high. Any unwritten register content data is lost if the I/O operation is aborted. Taking CSB low then resets the serial port controller and restarts the communication cycle.

#### **INSTRUCTION BYTE**

The instruction byte contains the information shown in the following bit map.

|   | MSB |    |    |    |    |    |    |    |  |

|---|-----|----|----|----|----|----|----|----|--|

| ſ | B7  | В6 | B5 | B4 | В3 | B2 | B1 | ВО |  |

| Ī | R/W | N1 | N0 | A4 | А3 | A2 | A1 | Α0 |  |

Bit 7, R/W, determines whether a read or a write data transfer occurs after the instruction byte write. Logic high indicates a read operation. Logic 0 indicates a write operation.

Bits<6:5>, N1 and N0, determine the number of bytes to be transferred during the data transfer cycle. The bits decode as shown in Table 13.

**Table 13. Byte Transfer Count**

| N1 | N0 | Description          |

|----|----|----------------------|

| 0  | 0  | Transfer one byte    |

| 0  | 1  | Transfer two bytes   |

| 1  | 0  | Transfer three bytes |

| 1  | 1  | Transfer four bytes  |

Bits<4:0>, A4, A3, A2, A1, and A0, determine which register is accessed during the data transfer of the communications cycle. For multibyte transfers, this address is a starting or ending address depending on the current data transfer mode. For MSB-first format, the specified address is an ending address or the most significant address in the current cycle. Remaining register addresses for multiple byte data transfers are generated

internally by the serial port controller by decrementing from the specified address. For LSB-first format, the specified address is a beginning address or the least significant address in the current cycle. Remaining register addresses for multiple byte data transfers are generated internally by the serial port controller by incrementing from the specified address.

#### MSB/LSB TRANSFERS

The serial port can support both MSB-first and LSB-first data formats. This functionality is controlled by Register 0x00, Bit 6. The default is Logic 0, which is MSB-first format.